DS-DM: Difference between revisions

| (149 intermediate revisions by the same user not shown) | |||

| Line 17: | Line 17: | ||

= Links = | = Links = | ||

* https://dsdaqgw.triumf.ca/vslice/ - vertical slice DAQ at TRIUMF | |||

* https://daq00.triumf.ca/DaqWiki/index.php/DarkSide - this DS-DAQ Wiki page | |||

* https://dsvslice.triumf.ca/vx_napoli - DS vertical slice at TRIUMF | * https://dsvslice.triumf.ca/vx_napoli - DS vertical slice at TRIUMF | ||

* https://edev-group.triumf.ca/hw/vme/dark-side-20k-data-manager-card/rev0 - DS-DM board Rev0 | |||

* https://edev-group.triumf.ca/hw/vme/dark-side-20k-data-manager-card/rev0 - | * https://edev-group.triumf.ca/hw/exp/dark-side-20k/cdm-gdm-data-manager-vme-cards/rev1 - DS-DM board Rev1 | ||

* https://edev-group.triumf.ca/hw/ | |||

* https://docs.xilinx.com/v/u/en-US/ds593 - Xilinx Platform Cable USB II | * https://docs.xilinx.com/v/u/en-US/ds593 - Xilinx Platform Cable USB II | ||

* https://www.enclustra.com/en/products/system-on-chip-modules/mercury-xu8/ - Enclustra | * https://www.enclustra.com/en/products/system-on-chip-modules/mercury-xu8/ - Enclustra | ||

* https://bitbucket.org/team-ds-dm/phasemeasurement - VX Phase measurement script | * https://bitbucket.org/team-ds-dm/phasemeasurement - VX Phase measurement script | ||

* https:// | * https://daq00.triumf.ca/daqinv/frontend/list/178 - inventory database | ||

* https://daq00.triumf.ca/elog-ds/DS-DAQ - DS-DAQ elog | * https://daq00.triumf.ca/elog-ds/DS-DAQ - DS-DAQ elog | ||

* https://edev-group.triumf.ca/hw/exp/dark-side-20k/dark-side-iogc/rev0 - GPS and Rb Clock adapter board | |||

= Git repos = | |||

* dsdmdev@dsdaqgw.triumf.ca:git/gcdm.git - git repository, DS-DM firmware, branch develop_ko2, contact K.O. for ssh key access | |||

* https://edev-group.triumf.ca/fw/exp/darkside/gcdm - git repository, DS-DM firmware (broken, do not use) | |||

* https://bitbucket.org/team-ds-dm/ds-dm-software - git repository, DS-DM MIDAS frontend | |||

* https://bitbucket.org/ttriumfdaq/dsproto_vx2740/src/develop/ - VX DSFE MIDAS frontend | * https://bitbucket.org/ttriumfdaq/dsproto_vx2740/src/develop/ - VX DSFE MIDAS frontend | ||

* https:// | * https://openproject.triumf.ca/svn/darkside-20k/ - VX firmware project | ||

= Onboard hardware = | = Onboard hardware = | ||

| Line 174: | Line 178: | ||

* [[File:SCH-DS-xDM-Rev1.PDF]] | * [[File:SCH-DS-xDM-Rev1.PDF]] | ||

* ENC-A is J800, ENC-B is J801, ENC-C is J900 | |||

* modifications from Rev0: | |||

* clocks: | |||

** 125MHz osc: CLK_XO_125, CLK3_XO_125 (CLK2_XO_125 removed) | |||

** C.C. in2 is CLK_CC_IN from ENC-C142,144 | |||

** C.C. out0 via CLK_A to CLK_CC_OUT0 (ENC-C3,5), CLK_CC_OUT1 (ENC-B3,5), CLK_CC_OUT2 (ENC-C151,153) | |||

* RTC chip: TP_S pins gone, RTC_I2C_SCL, RTC_I2C_SDA, RTC_1PPS and RTC_32KHZ added | |||

** RTC_1Hz ENC-C160 pull up 10k to 3.3V | |||

** RTC_32k ENC-B129 pull up 10k to 1.8V | |||

* QSFP, SFP control lines: | |||

** HW_ID_xDM ENC-B131 gone, reused as SFP_ModPrsN | |||

** SFP_ModPrsN (MOD_ABS) ENC-B131 input (no pulls) | |||

** SFP_TX_fault (was QSFP2_SEL) QSFP_ModPrsN ENC-C157 input (no pulls) | |||

** SFP_TX_disable from QSFP_LPMode ENC-C163 output (pull up 10k to 3.3V) | |||

** SFP_ModDet n/c (was QSFP_ModPrsN) renamed SFP_ModPrsN input | |||

** SFP_RX_LOS to QSFP_IntN ENC-C159 input (pull up 2k2 to 3.3V) | |||

** SFP_RS0, SFP_RS1 n/c, assembly option: floating | |||

** QSFP_ResetN - FPGA output, pull up 10k to 3.3V | |||

** QSFP0_SEL, QSFP1_SEL, QSFP2_SEL, QSFP3_SEL - FPGA outputs, pull up 10k to 3.3V | |||

** QSFP_LPmode - FPGA output, pull up 10k to 3.3V | |||

** QSFP_ModPrsN - ??? - pull up 2k2 to 3.3V | |||

** QSFP_IntN - ??? - pull up 2k2 to 3.3V | |||

* VX_TX and VX_RX reassigned for better length matching | |||

* cosmetic changes: | |||

** front panel USB-C connector (replaces Micro-USB) | |||

** (reset push button PB1 PORn ENC-A132 aka PS_POR_B aka PS_POR#) | |||

** (reset push button PB2 SRSTn ENC-A124 aka PS_SRST_B aka PS_SRST#) | |||

** front panel PB3 HRSTn same as PB1 | |||

* Enclustra errata: | |||

** possible cross talk between pins AA2 (J801-B90, VX9_RX2) and AE3 (J801-B129, RTC_32KHZ). no RTC on the CDM. | |||

** ethernet link up failure (see Microchip KSZ9031 errata) | |||

= FPGA MGT blocks = | = FPGA MGT blocks = | ||

| Line 264: | Line 299: | ||

Simplified: | Simplified: | ||

* 125 MHz osc -> CLK_XO_125 -> MGTREFCLK0_A -> not used | * 125 MHz osc -> CLK_XO_125 -> MGTREFCLK0_A -> clk_xo_125. not used | ||

* 125 MHz osc -> CLK3_XO_125 -> MGTREFCLK1_B -> SFP RX ref clock | * 125 MHz osc -> CLK3_XO_125 -> MGTREFCLK1_B -> CDM SFP RX ref clock | ||

* 125 MHz osc -> C.C. in1 | * 125 MHz osc -> C.C. in1 | ||

* C.C. in0 <- CLK_EXT1 (10 MHz GPS clock) | * C.C. in0 <- CLK_EXT1 (10 MHz GPS clock) | ||

* C.C. in1 <- 125 MHz osc | * C.C. in1 <- 125 MHz osc | ||

* C.C. in2 <- CLK_CC_IN <- FPGA AK9,AK8 <- SFP RX recovered clock, 125 MHz | * C.C. in2 <- CLK_CC_IN <- FPGA AK9,AK8 <- CLK_CC_IN1, rx_clk_mgt, SFP RX recovered clock, 125 MHz | ||

* C.C. in3 <- CLK_FB | * C.C. in3 <- CLK_FB | ||

* C.C. 125 MHz -> CLK_CC_OUT0 -> MGTREFCLK0_B -> QSFP RX and TX ref clock | * C.C. 125 MHz -> CLK_CC_OUT0 -> MGTREFCLK0_B -> GDM QSFP RX and TX ref clock, CDM rx_clk mux | ||

* C.C. 125 MHz -> CLK_CC_OUT1 -> MGTREFCLK1_D -> SFP TX clock | * C.C. 125 MHz -> CLK_CC_OUT1 -> MGTREFCLK1_D -> SFP TX clock | ||

* C.C. 125 MHz -> CLK_CC_OUT2 -> FPGA AG8,AH8 (GC) -> not used | * C.C. 125 MHz -> CLK_CC_OUT2 -> FPGA AG8,AH8 (GC) -> not used | ||

| Line 291: | Line 326: | ||

in0 <- CLK_EXT1 (GPS 10 MHz clock) | in0 <- CLK_EXT1 (GPS 10 MHz clock) | ||

in1 <- 125 MHz oscillator via U5 | in1 <- 125 MHz oscillator via U5 | ||

in2 <- CLK_CC_IN <- ENC C142,C144 <- FPGA AK9,AK8 <- XDC GDM missing, CDM | in2 <- CLK_CC_IN <- ENC C142,C144 <- FPGA AK9,AK8 <- XDC GDM missing, CDM CLK_CC_IN1 <- VHDL rx_clk_mgt | ||

in3 <- CLK_FB | in3 <- CLK_FB | ||

| Line 302: | Line 337: | ||

Q0 -> not used | Q0 -> not used | ||

Q1 -> CLK_CC_OUT0 -> ENC C3,C5 -> FPGA L8,L7 MGTREFCLK0_B -> XDC GDM clk_mgtrefclk0_x0y1_p, CDM | Q1 -> CLK_CC_OUT0 -> ENC C3,C5 -> FPGA L8,L7 MGTREFCLK0_B -> XDC GDM clk_mgtrefclk0_x0y1_p, CDM i_CLK_CC_OUT0_P -> VHDL GDM mgt_b_ref_clk QSFP RX and TX reference clocks, CDM alternate rx_clk via clock mux | ||

Q2 -> CLK_CC_OUT1 -> ENC B3,B5 -> FPGA B10,B9 MGTREFCLK1_D -> XDC | Q2 -> CLK_CC_OUT1 -> ENC B3,B5 -> FPGA B10,B9 MGTREFCLK1_D -> XDC i_CLK_CC_OUT1_P -> VHDL GDM not used, CDM mgt_tx_ref_clk SFP TX clock | ||

Q3 -> CLK_CC_OUT2 -> ENC C151,C153 -> FPGA AG8,AH8 (GC) -> XDC GDM, CDM | Q3 -> CLK_CC_OUT2 -> ENC C151,C153 -> FPGA AG8,AH8 (GC) -> XDC GDM missing, CDM i_CLK_CC_OUT2_P | ||

Q4 -> not used | Q4 -> not used | ||

Q5 -> SMA J9/J10 | Q5 -> SMA J9/J10 | ||

CLK_TP0 <-> ENC C69,C71 <-> FPGA N8,N7 MGTREFCLK1_A (not used) -> XDC CLK_TP0_P -> VHDL not used (DS-DM SMA J11, J12) | CLK_TP0 <-> ENC C69,C71 <-> FPGA N8,N7 MGTREFCLK1_A (not used) -> XDC CLK_TP0_P -> VHDL not used (DS-DM SMA J11, J12) | ||

disconnected <- OLD_CLK_CC_IN <- ENC B10,B12 <- FPGA D9,D10 MGTREFCLK0_D <- XDC o_CLK_CC_IN <- VHDL CDM o_OLD_CLK_CC_IN SFP o_mgt_rx_rec_clk | |||

Notes: | Notes: | ||

| Line 532: | Line 569: | ||

= Checklist for newly build boards = | = Checklist for newly build boards = | ||

== setup and boot == | |||

* put new board on workbench | * put new board on workbench | ||

* check - vme connector present, vme extraction handles present | * check - vme connector present, vme extraction handles present | ||

* check - standoff are removed from all thru-holes | * check - standoff are removed from all thru-holes | ||

* plug Enclustra module | * plug Enclustra module | ||

* check - SW1 both switches are in the "6" and "3" positions | |||

* check - SW6 both switches are in the "PS" position | * check - SW6 both switches are in the "PS" position | ||

* connect micro-usb cable from linux PC | * Rev0: connect micro-usb cable from linux PC | ||

* Rev1: connect usb-C cable from linux PC (USB C-to-C or C-to-A) | |||

* connect ethernet from 1gige capable network switch | * connect ethernet from 1gige capable network switch | ||

* connect power from lab power supply - GND, +5V and -12V nominal, +5.7V and -12.5V actual | * connect power from lab power supply - GND, +5V and -12V nominal, +5.7V and -12.5V actual | ||

* power up, +5V current 2.10-2.8A, -12V current 0.05A | * power up, +5V current 2.10-2.8A, -12V current 0.05A | ||

* on linux PC, open a new terminal, run: minicom -D /dev/ttyACM0 | * on linux PC, open a new terminal, run: minicom -D /dev/ttyACM0 -b 115200 | ||

* in minicom window, observe messages about Xilinx first stage boot loader, etc | * in minicom window, observe messages about Xilinx first stage boot loader, etc | ||

* on the ethernet switch, observe network link is 1gige speed (not 10mbit, not 100mbit). | * on the ethernet switch, observe network link is 1gige speed (not 10mbit, not 100mbit). | ||

* if everything boots okey, there will be a login prompt, login as root, password root. | * if everything boots okey, there will be a login prompt, login as root, password root. | ||

* alternatively, from root@daq13: ssh root@dsdm | |||

* busybox devmem 0x80010000 # read firmware version number, i.e. 0xEDAD0A77 | * busybox devmem 0x80010000 # read firmware version number, i.e. 0xEDAD0A77 | ||

== test i2c == | |||

* check i2c: (no SFP, no QSFP plugged in!) | |||

= | |||

* check | |||

<pre> | <pre> | ||

root@dsdm:~# i2cdetect -y -r 0 | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f | |||

00: -- -- -- -- -- -- -- -- | |||

10: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- | |||

20: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- | |||

30: -- -- -- 33 -- -- -- -- -- -- -- -- -- -- -- -- | |||

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- 4e -- | |||

50: -- -- -- 53 -- -- -- -- -- -- -- 5b -- -- -- -- | |||

60: -- -- -- -- -- -- -- -- -- -- -- 6b -- -- -- -- | |||

70: -- -- -- -- -- -- -- -- | |||

root@dsdm:~# | |||

</pre> | </pre> | ||

* test clock chip: | |||

<pre> | <pre> | ||

root@ | root@dsdm:~# ./test_cdm_local.exe --load-cc | ||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

DS-DM firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

Loading CC registers... | |||

Clock chip data block size 519 | |||

root@dsdm:~# ./test_cdm_local.exe --cc | |||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

DS-DM firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

Polling CC status... | |||

Clock chip state 1, status: LOS_IN0 OOF_IN0 IN1 IN_SEL_1 | |||

Ctrl-C | |||

</pre> | |||

* test RTC: | |||

root@ | <pre> | ||

root@dsdm:~# ./test_cdm_local.exe --rtc-read | |||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

DS-DM firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

Read the RTC chip! | |||

reg 0x00: 0 0 1 0 0 1 1 0 0x26 | |||

reg 0x01: 0 0 1 1 1 0 0 1 0x39 | |||

reg 0x02: 0 0 0 0 0 1 1 1 0x07 | |||

reg 0x03: 0 0 0 0 0 0 1 0 0x02 | |||

reg 0x04: 0 0 0 0 0 0 1 0 0x02 | |||

reg 0x05: 0 0 0 0 0 0 0 1 0x01 | |||

reg 0x06: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x07: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x08: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x09: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x10: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x11: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x12: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x13: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x14: 0 0 0 1 1 0 0 0 0x18 | |||

reg 0x15: 0 0 0 0 1 0 0 0 0x08 | |||

reg 0x16: 0 0 0 0 0 0 0 0 0x00 | |||

root@ | reg 0x17: 0 0 0 1 0 1 1 1 0x17 | ||

reg 0x18: 0 1 0 0 0 0 0 0 0x40 | |||

seconds: 26, minutes: 39, hours: 07, day 2, date: 00-01-02, temp 23.25C | |||

root@dsdm:~# | |||

</pre> | </pre> | ||

== test clocks == | |||

<pre> | <pre> | ||

root@ | root@dsdm:~# ./test_cdm_local.exe --reset-mgt | ||

... | |||

root@dsdm:~# ./test_cdm_local.exe --gdm-clocks | |||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

DS-DM firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

GDM clock frequency counters: | |||

50: -- -- -- | 0x1030 mgt_rx_ref_clk_raw: 0x07735cb9 (125000889) should be ~125 MHz | ||

0x1034 rx_clk: 0x07735cb9 (125000889) should be ~125 MHz | |||

0x1038 mgt_tx_ref_clk_raw: 0x07735cb9 (125000889) should be ~125 MHz | |||

root@ | 0x103C tx_clk: 0x07735cb9 (125000889) should be ~125 MHz | ||

0x1040 clk_50MHz: 0x02faf080 (50000000) should be 50 MHz exactly | |||

0x1044 Block1_clk: 0x05f5e100 (100000000) should be 100 MHz exactly | |||

^C | |||

root@dsdm:~# ./test_cdm_local.exe --cdm-clocks | |||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

DS-DM firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

CDM clock frequency counters: | |||

0x1030 mgt_rx_ref_clk_raw: 0x07735c6a (125000810) should be ~125 MHz | |||

0x1034 rx_clk: 0x07735c69 (125000809) should be ~125 MHz | |||

0x1038 mgt_tx_ref_clk_raw: 0x07735c69 (125000809) should be ~125 MHz | |||

0x103C tx_clk: 0x07735c6a (125000810) should be ~125 MHz | |||

0x1040 clk_50MHz: 0x02faf080 (50000000) should be 50 MHz exactly | |||

0x1044 Block1_clk: 0x05f5e100 (100000000) should be 100 MHz exactly | |||

^C | |||

root@dsdm:~# | |||

</pre> | </pre> | ||

== test LED, LEMO == | |||

* test LEDs, observe all 4 LEDs turn on and off every 1 second | |||

<pre> | <pre> | ||

root@ | root@dsdm:~# ./test_cdm_local.exe --blink-led | ||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

DS-DM firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

LED on | |||

LED off | |||

</pre> | |||

* TBW - test LEMO outputs | |||

<pre> | |||

have test firmware lemo outputs are RTC chip 1pps and 48kHz | |||

see them on the scope | |||

</pre> | |||

* TBW - test LEMO inputs | |||

<pre> | |||

./test_cdm_local.exe --monreg 6 | |||

</pre> | </pre> | ||

* | == test VX == | ||

* | |||

* | * on the CDM, connect all split blue cables to VX modules | ||

* set all VX modules to LVDS loopback mode (in VX settings MIDAS page) | |||

* ssh root@cdm00 | |||

* run "./test_cdm.exe --test-vx", it should report: | |||

<pre> | |||

CDM registers: 0x0000000000000000 0x00000000: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000eeeeeeeeeeee 0x00007700: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000080808080808 0x00000100: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000040404040404 0x00000200: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000020202020202 0x00000400: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000000000000000 0x00000800: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000808080808080 0x00001000: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000404040404040 0x00002000: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000202020202020 0x00004000: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

CDM registers: 0x0000000000000000 0x00008000: port0 ok port1 ok port2 ok port3 ok port4 ok port5 ok | |||

all on! | |||

all off! | |||

</pre> | |||

* on the VX settings MIDAS page LVDS input section, observe line status is cycling on and off. | |||

* note: VX_RX(0) is not tested by this, corresponding VX_TX is used as the VX clock | |||

== test SFP (CDM) == | |||

* connect SFP module | |||

* ssh root@cdm00 | |||

* run "./test_cdm.exe --sfp", it should report: | |||

<pre> | <pre> | ||

root@ | root@cdm00:~# ./test_cdm.exe --sfp | ||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x6a332b58, ds20k version 0x20241209 | |||

0x03 | DS-DM firmware build 0x6a332b58, ds20k version 0x20241209 | ||

Polling SFP status... | |||

identifier 0x03 | |||

connector 0x07 | |||

encoding 0x01 | |||

.. | wavelength 0x0352 (850 nm) | ||

vendor_name [FINISAR CORP. ] | |||

vendor_pn [FTLF8526P3BNL ] | |||

vendor_rev [A ] | |||

vendor_sn [N3AB4LV ] | |||

vendor_date [200319 ] | |||

dm_type 0x68 | |||

temp 30.9 C | |||

vcc 3.285 V | |||

tx_bias 7.362 mA | |||

tx_power 475.7 uW | |||

rx_power 859.1 uW | |||

SFP good 1, status: temp 30.9 C, tx_bias 7.4 mA, tx_power 476 uW, rx_power 859 uW | |||

SFP good 1, status: temp 30.8 C, tx_bias 7.4 mA, tx_power 475 uW, rx_power 859 uW | |||

SFP good 1, status: temp 30.8 C, tx_bias 7.4 mA, tx_power 476 uW, rx_power 859 uW | |||

SFP good 1, status: temp 30.7 C, tx_bias 7.4 mA, tx_power 476 uW, rx_power 859 uW | |||

SFP good 1, status: temp 30.8 C, tx_bias 7.4 mA, tx_power 475 uW, rx_power 858 uW | |||

^C | |||

root@cdm00:~# | |||

</pre> | </pre> | ||

* NOTE1: if fiber cable is disconnected or GDM is not running, rx_power would read 0 uW | |||

* NOTE2: better SFP modules have smaller tx_bias and larger tx_power (more bang for the buck) | |||

* NOTE3: bad fiber cable and bad fiber connection will result in smaller rx_power | |||

== test QSFP (GDM) == | |||

* connect QSFP module (any slot) | |||

* ssh root@gdm01 | |||

* run "./test_cdm.exe --qsfp3 --qsfp", try --qsfp0, --qsfp1, --qsfp2, --qsfp3 for the 4 QSFP slots | |||

<pre> | <pre> | ||

root@ | root@gdm01:~# ./test_cdm.exe --qsfp3 --qsfp | ||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x9e30baf9, ds20k version 0x20241209 | |||

DS-DM firmware build 0x9e30baf9, ds20k version 0x20241209 | |||

gpiochip0: GPIOs 338-511, parent: platform/ff0a0000.gpio, zynqmp_gpio: | |||

gpio-378 ( |sysfs ) out hi | |||

gpio-379 ( |sysfs ) out hi | |||

gpio-381 ( |sysfs ) out lo | |||

gpio-382 ( |sysfs ) out hi | |||

Polling QSFP status... | |||

identifier 0x0d | |||

status 0x02 | |||

los 0x89 | |||

temp 36.7 C | |||

vcc 3.302 V | |||

rx_power 0.1 413.7 460.3 0.1 uW | |||

tx_bias 7.8 7.9 7.9 0.0 mA | |||

tx_power 806.0 842.9 865.2 0.1 uW | |||

vendor_name [FINISAR CORP ] | |||

vendor_pn [FTL410QD4C ] | |||

vendor_rev [A ] | |||

wavelength 850 | |||

max_temp 70 C | |||

vendor_sn [X79AC0R ] | |||

vendor_date [220309 ] | |||

QSFP good 1, status: temp 36.7 C, los 0x89, tx_bias 7.8 7.9 7.9 0.0 mA, tx_power 806 843 865 0 uW, rx_power 0 414 460 0 uW | |||

^C | |||

</pre> | </pre> | ||

* NOTE1: 4th tx_bias and tx_power are zero because 4th channel does not transmit any data, QSFP detects this and automatically shuts down the optical transmitter | |||

* | = Serial console = | ||

* check that linux computer has correct udev rules to allow access to /dev/ttyACM devices, see https://daq00.triumf.ca/DaqWiki/index.php/SLinstall#Configure_USB_device_permissions and https://daq00.triumf.ca/DaqWiki/index.php/Ubuntu#Configure_USB_device_permissions | |||

* connect micro-USB cable to connector J-UCB, other end connect to linux computer | |||

* observe /dev/ttyACM0 was created | |||

* run "minicom -D /dev/ttyACM0 -b 115200" | |||

* should have gdm-cdm login | |||

* username root, password root | |||

= i2c = | |||

<pre> | <pre> | ||

ZynqMP> i2c bus | |||

Bus 0: i2c@ff020000 | |||

ZynqMP> i2c dev 0 | |||

Setting bus to 0 | |||

ZynqMP> i2c probe | |||

Valid chip addresses: 33 4E 53 5B 6B 77 | |||

00 | ZynqMP> i2c md 0x5b 0x98 | ||

10 | 0098: fc c2 3d 00 00 12 1a 6e 0a 90 85 04 94 10 08 50 ..=....n.......P | ||

</pre> | </pre> | ||

<pre> | <pre> | ||

root@ | root@gdm-cdm:~# i2cdetect 0 | ||

Warning: Can't use SMBus Quick Write command, will skip some addresses | |||

WARNING! This program can confuse your I2C bus, cause data loss and worse! | |||

I will probe file /dev/i2c-0. | |||

I will probe address range 0x03-0x77. | |||

Continue? [Y/n] | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f | |||

00: | |||

10: | |||

20: | |||

30: -- -- -- 33 -- -- -- -- | |||

40: | |||

50: -- -- -- 53 -- -- -- -- -- -- -- 5b -- -- -- -- | |||

60: | |||

70: | |||

root@gdm-cdm:~# | |||

root@gdm-cdm:~# i2cdump 0 0x5b | |||

No size specified (using byte-data access) | |||

WARNING! This program can confuse your I2C bus, cause data loss and worse! | |||

I will probe file /dev/i2c-0, address 0x5b, mode byte | |||

Continue? [Y/n] | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | 0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | ||

00: | 00: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | ||

10: | 10: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | ||

20: | 20: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | ||

30: | 30: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | ||

40: | 40: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | ||

50: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

60: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

70: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

80: 0a 90 85 04 94 10 08 50 90 5b a0 00 a0 00 00 00 ???????P?[?.?... | |||

90: 00 00 00 00 00 00 00 00 fc c2 3d 00 00 12 1a 6e ........??=..??n | |||

a0 | a0: 0a 90 85 04 94 10 08 50 90 5b a0 00 a0 00 00 00 ???????P?[?.?... | ||

b0: 00 00 00 00 00 00 00 00 fc c2 3d 00 00 12 1a 6e ........??=..??n | |||

c0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

d0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

e0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

f0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

root@gdm-cdm:~# | |||

b0: 00 00 00 00 00 00 00 00 00 00 | |||

c0: | |||

d0: | |||

e0: | |||

f0: | |||

root@ | |||

</pre> | </pre> | ||

<pre> | <pre> | ||

root@gdm0:~# i2cdetect -r 0 | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f | |||

00: -- -- -- -- -- -- -- -- | |||

10: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- | |||

20: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- | |||

30: -- -- -- 33 -- -- -- -- -- -- -- -- -- -- -- -- | |||

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- 4e -- | |||

50: -- -- -- 53 -- -- -- -- -- -- -- 5b -- -- -- -- | |||

60: -- -- -- -- -- -- -- -- -- -- -- 6b -- -- -- -- | |||

70: -- -- -- -- -- -- -- -- | |||

root@gdm0:~# | |||

</pre> | </pre> | ||

<pre> | <pre> | ||

root@cdm0:~# i2cdetect -r 0 | |||

root@ | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f | 0 1 2 3 4 5 6 7 8 9 a b c d e f | ||

00: -- -- -- -- -- -- -- -- | 00: -- -- -- -- -- -- -- -- | ||

| Line 837: | Line 884: | ||

30: -- -- -- 33 -- -- -- -- -- -- -- -- -- -- -- -- | 30: -- -- -- 33 -- -- -- -- -- -- -- -- -- -- -- -- | ||

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- 4e -- | 40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- 4e -- | ||

50: | 50: 50 51 -- 53 -- -- -- -- -- -- -- 5b -- -- -- -- | ||

60: -- -- -- -- -- -- -- -- -- -- -- 6b -- -- -- -- | 60: -- -- -- -- -- -- -- -- -- -- -- 6b -- -- -- -- | ||

70: -- -- -- -- -- -- -- -- | 70: -- -- -- -- -- -- -- -- | ||

root@ | root@cdm0:~# | ||

</pre> | |||

* 0x33 - XU8 secure EEPROM (should be at 0x32) | |||

* 0x4e - U23 current and temperature monitor | |||

* 0x50, 0x51 - SFP | |||

* 0x50 - QSFP, 4 QSFP modules enabled by GPIO QSFP0_SEL, QSFP1_SEL, QSFP2_SEL, QSFP3_SEL | |||

* 0x53, 0x5b - ethernet mac eeprom | |||

* 0x6b - U6 clock chip | |||

== U23 == | |||

NOTE: Text reads double of Tint. not sure why. K.O. 21-mar-2024. | |||

* internal temperature only | |||

<pre> | |||

root@gdm0:~# i2cset -y 0 0x4e 0x01 0x00 b # control register: "repeat mode, internal temperature only" | |||

root@gdm0:~# i2cset -y 0 0x4e 0x02 0xff b # trigger | |||

root@gdm0:~# i2cget -y 0 0x4e 0x00 b # status register | |||

0x03 # "Tint ready" and "busy", "busy is always 1 in repeat mode" | |||

root@gdm0:~# i2cdump -y 0 0x4e b | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | |||

00: 03 00 03 03 81 db 2a ce 2a 8e 00 6f 00 45 20 3f ?.????*?*?.o.E ? | |||

10: 01 00 01 01 01 db 2a ce 2a 8e 00 6f 00 45 20 3f ?.????*?*?.o.E ? | |||

... | |||

readback: | |||

reg0 - 03 - Tint ready | |||

reg1 - 00 - what we put there | |||

reg2 - trigger | |||

reg3 - not used | |||

reg4 - Tint MSB 0x81, bit 0x80 is "DV, data valid", bit 0x40 is "SS, sensor short", 0x20 is "SO, sensor open" | |||

reg5 - Tint LSB 0xDB, Tint = 0x01DB = 475 * 0.0625 degC = 29.6 degC | |||

reg6..F - stale data | |||

</pre> | </pre> | ||

* Tint, V1, V2, TR2, VCC | |||

<pre> | <pre> | ||

root@ | root@gdm0:~# i2cset -y 0 0x4e 0x01 0x18 b # control register: "repeat mode, V1, V2, TR2" | ||

root@gdm0:~# i2cset -y 0 0x4e 0x02 0xff b # trigger | |||

root@gdm0:~# i2cget -y 0 0x4e 0x00 b # status register | |||

0x7f # all data is ready | |||

root@gdm0:~# i2cdump -y 0 0x4e b | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | 0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | ||

00: | 00: 7f 18 7f 7f 81 b9 aa d0 aa 8f 83 5e 83 5e a0 41 ???????????^?^?A | ||

10: | 10: 01 18 01 01 01 b9 2a d0 2a 8f 03 5e 03 5e 20 41 ??????*?*??^?^ A | ||

reg0 - 7F - all data ready | |||

reg1 - 18 - what we put there | |||

reg2 - trigger | |||

reg3 - not used | |||

reg4 - Tint MSB and DV, SS, SO. | |||

reg5 - Tint LSB 0x1b9*0.0625 = 27.5 degC | |||

reg6 - V1 MSB 0xaa, bit 0x80 is DV, bit 0x40 is sign | |||

reg7 - V1 LSB 0xd0, V1 = 0x2ad0*305.18/1000000 = 3.3447 V (correct) | |||

reg8 - V2 MSB 0xaa, ditto | |||

reg9 - V2 LSB 0x8f, V2 = 0x2a8f*305.18/1000000 = 3.3249 V (correct, smaller than V1) | |||

regA - V3 MSB or TR2 MSB 0x83, 0x80=DV, 0x40=SS, 0x20=SO | |||

regB - V3 LSB or TR2 LSB 0x5e. TR2 = 0x35e*0.0625 = 53.875 degC (wrong, thermistor Q5 is next to U23, should read same as Tint) | |||

regC - V4 MSB or TR2 MSB | |||

regD - V4 LSB or TR2 LSB | |||

regE - VCC MSB 0xa0, bit 0x80 is DV, 0x40 is sign | |||

regF - VCC LSB 0x41, VCC = 2.5+0x2041*305.18/1000000 = 5.019 V (correct, VCC is +5V) | |||

3V3_SW current is (V2-V1)/0.020 = 0.99 A (about right?) | |||

</pre> | |||

* Tint, V1-V2, TR2, VCC | |||

root@ | <pre> | ||

root@gdm0:~# i2cset -y 0 0x4e 0x01 0x19 b # control register: "repeat mode, V1-V2, TR2" | |||

root@gdm0:~# i2cset -y 0 0x4e 0x02 0xff b # trigger | |||

root@gdm0:~# i2cget -y 0 0x4e 0x00 b # status register | |||

0x7f # all data is ready | |||

root@gdm0:~# i2cdump -y 0 0x4e b | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | 0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | ||

00: | 00: 7f 19 7f 7f 81 69 83 f2 83 f2 83 3a 83 3a a0 44 ?????i?????:?:?D | ||

10: 01 19 01 01 01 69 03 f2 03 f2 03 3a 03 3a 20 44 ?????i?????:?: D | |||

reg0 - 7F - all data ready | |||

reg1 - 18 - what we put there | |||

reg2 - trigger | |||

reg3 - not used | |||

reg4 - Tint MSB and DV, SS, SO. | |||

reg5 - Tint LSB 0x169*0.0625 = 22.5 degC | |||

reg6 - V1 or V1-V2 MSB 0x83, bit 0x80 is DV, bit 0x40 is sign | |||

reg7 - V1 or V1-V2 LSB 0xf2, V1-V2 = 0x3f2*19.42/1000000 = 0.0196142 V (correct, compare with V1 and V2 measured above) | |||

reg8 - V2 or V1-V2 MSB | |||

reg9 - V2 or V1-V2 LSB | |||

regA - V3 MSB or TR2 MSB 0x83, 0x80=DV, 0x40=SS, 0x20=SO | |||

regB - V3 LSB or TR2 LSB 0x3a. TR2 = 0x33a*0.0625 = 51.625 degC (wrong, thermistor Q5 is next to U23, should read same as Tint) | |||

regC - V4 MSB or TR2 MSB | |||

regD - V4 LSB or TR2 LSB | |||

regE - VCC MSB 0xa0, bit 0x80 is DV, 0x40 is sign | |||

regF - VCC LSB 0x44, VCC = 2.5+0x2044*305.18/1000000 = 5.021 V (correct, VCC is +5V) | |||

3V3_SW current is (V2-V1)/0.020 = 0.9807 A (about right?) | |||

</pre> | </pre> | ||

== SFP == | |||

<pre> | <pre> | ||

root@cdm0:~# i2cdump 0 | root@cdm0:~# i2cdump 0 0x50 | ||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | 0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | ||

00: | 00: 03 04 07 00 00 00 00 40 40 0c 00 01 3d 00 00 00 ???....@@?.?=... | ||

10: | 10: 0c 02 00 1e 46 49 4e 49 53 41 52 20 43 4f 52 50 ??.?FINISAR CORP | ||

20: | 20: 2e 20 20 20 00 00 90 65 46 54 4c 46 38 35 32 36 . ..?eFTLF8526 | ||

30: | 30: 50 33 42 4e 4c 20 20 20 41 20 20 20 03 52 00 9d P3BNL A ?R.? | ||

40: | 40: 00 1a 00 00 4e 33 41 42 34 4c 56 20 20 20 20 20 .?..N3AB4LV | ||

50: | 50: 20 20 20 20 32 30 30 33 31 39 20 20 68 f0 03 de 200319 h??? | ||

60: | 60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

70: | 70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

80: | 80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

90: | 90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

a0: | a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

b0: | b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

c0: | c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

d0: | d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

e0: | e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

f0: | f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

root@cdm0:~# i2cdump 0 | root@cdm0:~# | ||

root@cdm0:~# i2cdump 0 0x51 | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | 0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | ||

00: | 00: 5a 00 d8 00 55 00 e2 00 90 88 71 48 8c a0 75 30 Z.?.U.?.??qH??u0 | ||

10: | 10: 21 34 01 f4 1b 58 03 e8 31 2d 04 eb 1f 07 06 31 !4???X??1-?????1 | ||

20: | 20: 31 2d 00 64 27 10 00 9e 00 00 00 00 00 00 00 00 1-.d'?.?........ | ||

30: | 30: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

40: 00 00 00 00 3f 80 00 00 00 00 00 00 01 00 00 00 ....??......?... | |||

50: 01 00 00 00 01 00 00 00 01 00 00 00 00 00 00 b7 ?...?...?......? | |||

60: 19 9f 80 c5 0e 17 12 c4 1f 99 00 00 00 00 30 00 ??????????....0. | |||

70: ff ff ff ff ff ff ff | 70: 00 00 00 00 00 00 00 00 ff ff ff ff ff ff ff 01 ...............? | ||

80: | 80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

90: 00 00 00 00 00 00 00 00 | 90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

a0: | a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

b0: 00 00 00 00 00 00 00 00 | b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

c0: | c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

d0: | d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

e0: | e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

f0: | f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | ||

root@cdm0:~# | root@cdm0:~# | ||

</pre> | </pre> | ||

= | == QSFP == | ||

<pre> | |||

QSFP i2c enable lines, active low: | |||

QSFP0_SEL - JENC-A 82 - PS-MIO40 - linux gpio 378 | |||

QSFP1_SEL - JENC-A 84 - PS-MIO41 - linux gpio 379 | |||

QSFP2_SEL - JENC-A 100 - PS-MIO44 - linux gpio 382 | |||

QSFP3_SEL - JENC-A 106 - PS-MIO43 - linux gpio 381 (notice 2 and 3 are out of order) | |||

</pre> | |||

<pre> | <pre> | ||

// | # cat /sys/kernel/debug/gpio | ||

gpiochip0: GPIOs 338-511, parent: platform/ff0a0000.gpio, zynqmp_gpio: | |||

# echo 378 >> /sys/class/gpio/export ### SEL0 338+40 | |||

# echo 379 >> /sys/class/gpio/export ### SEL1 338+41 | |||

# echo 381 >> /sys/class/gpio/export ### SEL3 338+43 | |||

# echo 382 >> /sys/class/gpio/export ### SEL2 338+44 | |||

# cat /sys/kernel/debug/gpio | |||

gpiochip0: GPIOs 338-511, parent: platform/ff0a0000.gpio, zynqmp_gpio: | |||

gpio-378 ( |sysfs ) in hi | |||

gpio-379 ( |sysfs ) in hi | |||

gpio-381 ( |sysfs ) in hi | |||

gpio-382 ( |sysfs ) in hi | |||

root@gdm0:~# echo out >> /sys/class/gpio/gpio381/direction | |||

root@gdm0:~# echo out >> /sys/class/gpio/gpio382/direction | |||

root@gdm0:~# echo out >> /sys/class/gpio/gpio378/direction | |||

root@gdm0:~# echo out >> /sys/class/gpio/gpio379/direction | |||

root@gdm0:~# | |||

root@gdm0:~# cat /sys/kernel/debug/gpio | |||

gpiochip0: GPIOs 338-511, parent: platform/ff0a0000.gpio, zynqmp_gpio: | |||

gpio-378 ( |sysfs ) out lo | |||

gpio-379 ( |sysfs ) out lo | |||

gpio-381 ( |sysfs ) out lo | |||

gpio-382 ( |sysfs ) out lo | |||

root@gdm0:~# | |||

echo 1 >> /sys/class/gpio/gpio381/value | |||

echo 1 >> /sys/class/gpio/gpio382/value | |||

echo 1 >> /sys/class/gpio/gpio378/value | |||

echo 1 >> /sys/class/gpio/gpio379/value | |||

cat /sys/kernel/debug/gpio | |||

root@gdm0:~# cat /sys/kernel/debug/gpio | |||

gpiochip0: GPIOs 338-511, parent: platform/ff0a0000.gpio, zynqmp_gpio: | |||

gpio-378 ( |sysfs ) out hi | |||

gpio-379 ( |sysfs ) out hi | |||

gpio-381 ( |sysfs ) out hi | |||

gpio-382 ( |sysfs ) out hi | |||

root@gdm0:~# | |||

root@gdm0:~# i2cdetect -y -r 0 | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f | |||

00: -- -- -- -- -- -- -- -- | |||

10: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- | |||

20: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- | |||

30: -- -- -- 33 -- -- -- -- -- -- -- -- -- -- -- -- | |||

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- 4e -- | |||

50: -- -- -- 53 -- -- -- -- -- -- -- 5b -- -- -- -- | |||

60: -- -- -- -- -- -- -- -- -- -- -- 6b -- -- -- -- | |||

70: -- -- -- -- -- -- -- -- | |||

root@gdm0:~# | |||

NOTICE NOTHING AT ADDRESS 0x50 | |||

</pre> | |||

<pre> | |||

ENABLE QSFP0, OBSERVE IT IS AT ADDRESS 0x50 | |||

root@gdm0:~# echo 0 >> /sys/class/gpio/gpio378/value | |||

root@gdm0:~# i2cdetect -y -r 0 | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f | |||

00: -- -- -- -- -- -- -- -- | |||

10: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- | |||

20: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- | |||

30: -- -- -- 33 -- -- -- -- -- -- -- -- -- -- -- -- | |||

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- 4e -- | |||

50: 50 -- -- 53 -- -- -- -- -- -- -- 5b -- -- -- -- | |||

60: -- -- -- -- -- -- -- -- -- -- -- 6b -- -- -- -- | |||

70: -- -- -- -- -- -- -- -- | |||

root@gdm0:~# | |||

root@gdm0:~# i2cdump -y 0 0x50 | |||

No size specified (using byte-data access) | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | |||

00: 0d 00 02 8e 00 00 01 00 00 05 55 00 05 00 00 00 ?.??..?..?U.?... | |||

10: 00 00 00 00 00 00 1e b8 00 00 81 a0 00 00 00 00 ......??..??.... | |||

20: 00 00 12 12 00 01 00 01 00 01 0e e0 0f 20 0e e0 ..??.?.?.???? ?? | |||

30: 00 00 1f a0 1e 3b 1f 72 00 01 00 00 00 00 00 00 ..???;?r.?...... | |||

40: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | |||

50: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | |||

60: 00 00 00 00 00 00 00 00 00 00 1f 00 00 00 08 00 ..........?...?. | |||

70: 00 00 00 00 00 00 00 ff ff ff ff ff ff ff ff 00 ................ | |||

80: 0d 00 0c 04 00 00 00 40 40 02 d5 05 67 00 00 96 ?.??...@@???g..? | |||

90: 00 00 c8 00 46 49 4e 49 53 41 52 20 43 4f 52 50 ..?.FINISAR CORP | |||

a0: 20 20 20 20 07 00 90 65 46 54 4c 34 31 30 51 44 ?.?eFTL410QD | |||

b0: 34 43 20 20 20 20 20 20 41 20 42 68 07 d0 00 43 4C A Bh??.C | |||

c0: 00 07 0f de 58 37 39 41 43 30 52 20 20 20 20 20 .???X79AC0R | |||

d0: 20 20 20 20 32 32 30 33 30 39 20 20 3c 10 00 9e 220309 <?.? | |||

e0: 20 20 20 20 20 20 20 20 20 20 20 20 20 20 20 20 | |||

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................ | |||

root@gdm0:~# | |||

</pre> | |||

== ethernet mac eeprom == | |||

* correct chip with 84-bit ethernet mac address | |||

<pre> | |||

root@cdm1:~# i2cdump 0 0x53 | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | |||

00: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

10: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

20: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

30: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

40: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

50: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

60: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

70: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

80: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

90: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

a0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

b0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

c0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

d0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

e0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

f0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

root@cdm1:~# | |||

root@cdm1:~# i2cdump 0 0x5b | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | |||

00: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

10: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

20: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

30: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

40: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

50: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

60: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

70: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

80: 0a 80 c2 04 34 10 08 32 a8 4b a0 00 a0 00 00 00 ????4??2?K?.?... | |||

90: 00 00 00 00 00 00 00 00 00 00 fc c2 3d 1a 51 3c ..........??=?Q< | |||

a0: 0a 80 c2 04 34 10 08 32 a8 4b a0 00 a0 00 00 00 ????4??2?K?.?... | |||

b0: 00 00 00 00 00 00 00 00 00 00 fc c2 3d 1a 51 3c ..........??=?Q< | |||

c0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

d0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

e0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

f0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

root@cdm1:~# | |||

</pre> | |||

* wrong "602" chip with 64-bit IPv6 address | |||

<pre> | <pre> | ||

root@cdm0:~# i2cdump 0 0x53 | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | |||

00: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

10: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

20: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

30: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

40: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

50: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

60: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

70: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

80: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

90: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

a0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

b0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

c0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

d0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

e0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

f0: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

root@cdm0:~# i2cdump 0 0x5b | |||

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef | |||

00: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

10: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

20: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

30: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

40: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

50: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

60: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

70: ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ................ | |||

80: 0a 90 85 04 94 10 08 51 10 5b a0 00 a0 00 00 00 ???????Q?[?.?... | |||

90: 00 00 00 00 00 00 00 00 fc c2 3d 00 00 12 1a 2e ........??=..??. | |||

a0: 0a 90 85 04 94 10 08 51 10 5b a0 00 a0 00 00 00 ???????Q?[?.?... | |||

b0: 00 00 00 00 00 00 00 00 fc c2 3d 00 00 12 1a 2e ........??=..??. | |||

c0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

d0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

e0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

f0: XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XXXXXXXXXXXXXXXX | |||

root@cdm0:~# | |||

</pre> | </pre> | ||

= read ethernet mac address from i2c ( | = read ethernet mac address from i2c = | ||

(this code is copied from uboot command line i2c code) | |||

in uboot sources board/xilinx/common/board.c replace original function with this: | |||

<pre> | <pre> | ||

// special code to read ethernet MAC address from the DS-DM-Rev0 board. K.O. Sep-2022 | |||

int zynq_board_read_rom_ethaddr(unsigned char *ethaddr) | |||

{ | |||

struct udevice *bus; | |||

int ret; | |||

int busnum = 0; | |||

ret = uclass_get_device_by_seq(UCLASS_I2C, busnum, &bus); | |||

if (ret) { | |||

printf("%s: No bus %d\n", __func__, busnum); | |||

return ret; | |||

} | |||

= | int chip_addr = 0x5B; | ||

struct udevice *dev; | |||

ret = i2c_get_chip(bus, chip_addr, 1, &dev); | |||

if (ret) { | |||

printf("%s: Bus %d no chip 0x%02x\n", __func__, busnum, chip_addr); | |||

return ret; | |||

} | |||

int dev_addr = 0x98; | |||

unsigned char data[8]; | |||

ret = dm_i2c_read(dev, dev_addr, data, 8); | |||

if (ret) { | |||

printf("%s: Bus %d chip 0x%02x read error %d\n", __func__, busnum, chip_addr, ret); | |||

return ret; | |||

} | |||

} | |||

printf("%s: Bus %d chip 0x%02x addr 0x%02x read: 0x %02x %02x %02x %02x %02x %02x %02x %02x\n", __func__, busnum, chip_addr, dev_addr, data[0], data[1], data[2], data[3], data[4], data[5], data[6], data[7]); | |||

// see Atmel-8807-SEEPROM-AT24MAC402-602-Datasheet.pdf | |||

if (data[0] == 0) { | |||

// eiu-48 chip | |||

ethaddr[0] = data[2]; | |||

ethaddr[1] = data[3]; | |||

ethaddr[2] = data[4]; | |||

ethaddr[3] = data[5]; | |||

ethaddr[4] = data[6]; | |||

ethaddr[5] = data[7]; | |||

} else { | |||

// eiu-64 chip | |||

ethaddr[0] = data[0]; | |||

ethaddr[1] = data[1]; | |||

ethaddr[2] = data[2]; | |||

ethaddr[3] = data[5]; | |||

ethaddr[4] = data[6]; | |||

ethaddr[5] = data[7]; | |||

} | |||

printf("%s: ethaddr %02x:%02x:%02x:%02x:%02x:%02x\n", __func__, ethaddr[0], ethaddr[1], ethaddr[2], ethaddr[3], ethaddr[4], ethaddr[5]); | |||

return ret; | |||

} | |||

</pre> | </pre> | ||

also this should have worked if i2c_xxx() functions were enabled in uboot: | |||

<pre> | <pre> | ||

i2c_set_bus_num(0); | |||

i2c_probe(0x5b); | |||

i2c_read(0x5b, 0x9a, ethaddr, 6); | |||

</pre> | </pre> | ||

= | = read ethernet mac address from i2c (SHOULD WORK) = | ||

from: https://stackoverflow.com/questions/43637540/is-there-linux-or-u-boot-support-to-read-a-mac-address-from-a-chip-at-startup | |||

<pre> | |||

#ethernet related setup | |||

setup_eth=run readmac buildmac | |||

#read mac address from eeprom | |||

readmac=i2c dev 0; i2c read 50 FA.1 6 $loadaddr | |||

#build the ethaddr variable | |||

#not very nice, but does the job | |||

buildmac=\ | |||

e=" "; sep=" " \ | |||

for i in 0 1 2 3 4 5 ; do\ | |||

setexpr x $loadaddr + $i\ | |||

setexpr.b b *$x\ | |||

e="$e$sep$b"\ | |||

sep=":"\ | |||

done &&\ | |||

setenv ethaddr $e | |||

</pre> | |||

from | = read ethernet mac address from i2c (DOES NOT WORK) = | ||

this method does not work: inside board/xilinx/common/board.c:int zynq_board_read_rom_ethaddr(unsigned char *ethaddr), uclass_get_device_by_ofnode(UCLASS_I2C_EEPROM, eeprom, &dev) returns ENODEV and read from i2c does not happen. K.O. Sep-2022 | |||

Read: | |||

* https://support.xilinx.com/s/question/0D52E00006hpKlsSAE/uboot-and-ethernet-mac-address-from-eeprom?language=en_US (last answer) | |||

* https://github.com/Xilinx/u-boot-xlnx/blob/master/board/xilinx/common/board.c (zynq_board_read_rom_ethaddr()) | |||

Note: | |||

* 0x5B is the i2c chip address | |||

* 0x9A is the data offset inside the chip, see datasheet or i2c read dump above. | |||

Edit: | |||

* emacs -nw PetaLinux_GDM_CDM/project-spec/meta-user/recipes-bsp/u-boot/files/platform-top.h | |||

<pre> | <pre> | ||

#include <configs/xilinx_zynqmp.h> | |||

#include <configs/platform-auto.h> | |||

//#define CONFIG_I2C_EEPROM | |||

//#define CONFIG_SYS_I2C_EEPROM_ADDR 0x5b | |||

//#define CONFIG_SYS_I2C_EEPROM_ADDR_OVERFLOW 0x0 | |||

#define CONFIG_ZYNQ_GEM_I2C_MAC_OFFSET 0x9A | |||

#error HERE! | |||

</pre> | |||

* emacs -nw PetaLinux_GDM_CDM/project-spec/meta-user/recipes-bsp/device-tree/files/system-user.dtsi | |||

<pre> | |||

/include/ "system-conf.dtsi" | |||

/ { | |||

chosen { | |||

xlnx,eeprom = &eeprom; | |||

}; | |||

}; | |||

&i2c0 { | |||

eeprom: eeprom@5b { /* u88 */ | |||

compatible = "atmel,24mac402"; | |||

reg = <0x5b>; | |||

}; | |||

}; | |||

</pre> | |||

* components/yocto/workspace/sources/u-boot-xlnx/configs/xilinx_zynqmp_virt_defconfig | |||

<pre> | |||

CONFIG_ZYNQ_GEM_I2C_MAC_OFFSET=0x9A | |||

</pre> | </pre> | ||

= RTC chip = | |||

* DS3231 RTC chip | |||

* FPGA connections: | |||

<pre> | |||

I2C SCL <- J-ENC A85 <- FPGA E17 <- XDC TP_S <- VHDL RTC_I2C_SCL output (10k pull-up to 3.3V) | |||

I2C SDA <-> J-ENC A87 <-> FPGA D17 <-> XDC TP_S <-> VHDL RTC_I2C_SDA bidir (10k pull-up to 3.3V) | |||

RTC_1Hz -> J-ENC C160 -> FPGA AH12 -> XDC "slow_io" -> VHDL RTC_1PPS input (10k pull-up to 1.2V) | |||

RTC_32k -> J-ENC B129 -> FPGA AE3 -> XDC "free pin" -> VHDL RTC_32KHZ input (10k pull-up to 1.8V) | |||

</pre> | |||

* test notes | |||

<pre> | <pre> | ||

FPGA registers: | |||

rtc_i2c_clock_ie <= not register_data_in_block_0(14)(0); | |||

rtc_i2c_clock_out <= register_data_in_block_0(14)(1); | |||

rtc_i2c_data_ie <= not register_data_in_block_0(14)(4); | |||

rtc_i2c_data_out <= register_data_in_block_0(14)(5); | |||

ext_out(1) <= rtc_1pps_in; | |||

ext_out(2) <= rtc_32khz_in; | |||

register_data_out_block_0(13) <= x"000000" & rtc_i2c_data_ie & rtc_i2c_data_out & rtc_i2c_clock_ie & rtc_i2c_clock_out & rtc_1pps_in & rtc_32khz_in & rtc_i2c_data_in & rtc_i2c_clock_in; | |||

After power us on the RTC chip: | |||

i2c clock 3.3V | |||

i2c data 3.3V | |||

32kHz 0.778V see clock running with amplitude 0->1.8V (FPGA pullup) period about 30 usec (~33 kHz) | |||

1pps 1.2V (FPGA pullup) | |||

./test1.exe --read32 0x34 | |||

dsdm_read32[0x00000034] is 0x000000ab (171) -> 1010'1011 -> data_ie, clock_ie, 1pps, data_in, clock_in | |||

./test1.exe --read32 0x38 | |||

dsdm_read32[0x00000038] is 0x00000000 (0) | |||

./test1.exe --write32 0x38 0x01 -> clock oe | |||

./test1.exe --read32 0x34 | |||

Ddsdm_read32[0x00000034] is 0x0000008a (138) -> 1000'1010 -> data_ie, 1pps, data_in, clock 0V, data 3.3V | |||

./test1.exe --write32 0x38 0x10 -> data_oe | |||

./test1.exe --read32 0x34 | |||

dsdm_read32[0x00000034] is 0x00000029 (41) -> 0010'1001 -> clock_ie, 1pps, clock_in, clock 3.3V, data 0V | |||

root@dsdm:~# ./test_cdm_local.exe --rtc-read | |||

DS-DM mapping /dev/mem at 0x80010000 | |||

DS-DM FPGA firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

DS-DM firmware build 0x0e30d3a8, ds20k version 0x20241104 | |||

Read the RTC chip! | |||

reg 0x00: 0 1 0 1 0 1 1 1 0x57 | |||

reg 0x01: 0 0 1 0 0 0 1 0 0x22 | |||

reg 0x02: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x03: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x04: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x05: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x06: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x07: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x08: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x09: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x10: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x11: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x12: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x13: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x14: 0 0 0 1 1 0 0 0 0x18 | |||

reg 0x15: 0 0 0 0 1 0 0 0 0x08 | |||

reg 0x16: 0 0 0 0 0 0 0 0 0x00 | |||

reg 0x17: 0 0 0 1 0 1 1 1 0x17 | |||

reg 0x18: 1 1 0 0 0 0 0 0 0xc0 | |||

seconds: 57, minutes: 22, hours: 00, day 0, date: 00-00-00, temp 23.75C | |||

root@dsdm:~# | |||

</pre> | </pre> | ||

= | = clock chip configuration = | ||

file CDM_v3.0_IN1_fixed_and_IN2_RX_Recovered_VX_62.5MHz_Si5394-RevA-Registers.txt: | |||

* VCO is 14 GHz | |||

* Tvco is 71.43 ps | |||

* N0 divider is 14, frequency is 1000 MHz | |||

* out0 from N0 divider 0x3 is (3+1)*2 = 8, freq 125 MHz | |||

* out1 from N0 divider 0x7 is (7+1)*2 = 16, freq 62.5 MHz | |||

* out2 from N0 divider 0x7 is (7+1)*2 = 16, freq 62.5 MHz | |||

* out3 from N0 divider 0x3 is (3+1)*2 = 8, freq 125 MHz is the feedback for zero delay | |||

= clock chip monitoring = | |||

from si5395-94-92-family.pdf: | |||

* reg 0x1: page select, set to 0 or set to 5 to read 0x53F | |||

* reg 0x2: 0x94 | |||

* reg 0x3: 0x53 -> device is a si5394 | |||

* | * reg 0xC: LOSXAXB | ||

* reg 0xD: LOS and OOF for the 4 clock inputs | |||

* reg 0xE: LOL and HOLD | |||

* reg 0xF: CAL_PLL | |||

* reg 0x11: sticky bits for reg 0xC | |||

* reg 0x12: sticky bits for reg 0xD | |||

* reg 0x13: sticky bits for reg 0xE | |||

* reg 0x14: sticky bits for reg 0xF | |||

* reg 0x1C: device reset | |||

* reg 0x1E: low power, hard reset, SYNC | |||

* reg 0x507: currently selected input clock | |||

* reg 0x52A: input clock select | |||

* reg 0x535: FORCE_HOLD | |||

* reg 0x53F: HOLD_HIST_VALID and FASTLOCK_STATUS | |||

= Install Xilinx tools = | |||

* install Vivado 2020.2 | |||

<pre> | <pre> | ||

login at https://www.xilinx.com/myprofile.html | |||

go to "Downloads" | |||

go to archive, | |||

find 2020.2 | |||

download Xilinx_Unified_2020.2_1118_1232_Lin64.bin | |||

sh ./Xilinx_Unified_2020.2_1118_1232_Lin64.bin | |||

banner window should open with spinner "downloading installation data" | |||

"a newer version is available" -> say "continue" | |||

next | |||

"select install type" window: | |||

provide email and password, | |||

select "download image" | |||

select directory /home/olchansk/Xilinx/Downloads/2020.2\ | |||

select "linux" and "full image" | |||

next | |||

download summary: space required 38.52 Gbytes | |||

download | |||

installation progress | |||

downloading spinner, 16 M/s 47 minutes... | |||

"download image has been created successfully". Ok. | |||

check contents of /home/olchansk/Xilinx/Downloads/2020.2 | |||

ls -l /home/olchansk/Xilinx/Downloads/2020.2 | |||

total 67 | |||

drwxr-xr-x 2 olchansk users 9 Sep 1 16:22 bin | |||

drwxr-xr-x 3 olchansk users 15 Sep 1 16:23 data | |||

drwxr-xr-x 4 olchansk users 4 Sep 1 16:22 lib | |||

drwxr-xr-x 2 olchansk users 644 Sep 1 16:22 payload | |||

drwxr-xr-x 2 olchansk users 7 Sep 1 16:22 scripts | |||

drwxr-xr-x 4 olchansk users 4 Sep 1 16:22 tps | |||

-rwxr-xr-x 1 olchansk users 3256 Nov 18 2020 xsetup | |||

daq13:2020.2$ | |||

./xsetup | |||

spinned loading installation data | |||

xilinx design tools 2022.1 now available -> say continue | |||

"welcome" -> next | |||

"select product" -> vivado -> next -> vivado hl system edition -> next | |||

select devices: only zynq ultrascale+ mpsoc -> next | |||

select destination: /opt/Xilinx (as root, mkdir /opt/Xilinx, chmod olchansk.users /opt/Xilinx) | |||

install ... | |||

complete | |||

move /home/olchansk/Xilinx/Downloads/2020.2 to /daq/daqstore/olchansk/Xilinx/Downloads/ | |||

</pre> | </pre> | ||

* | * install petalinux 2020.2 | ||

<pre> | <pre> | ||

./xsetup | |||

"a newer version is available" -> say "continue" | |||

next | |||

"select product to install" -> select Petalinux (Linux only) -> next | |||

petalinux- | "select destination directory" -> select "/opt/Xilinx" (disk space required 2.64 GB) -> next | ||

"summary" -> install ... | |||

error about missing /tmp/tmp-something files | |||

"installation completed successfully" (hard to dismiss, "ok" button is partially cut-off) | |||

done? | |||

I think it failed, /opt/Xilinx/PetaLinux/2020.2/bin is empty except for petalinux-v2020.2-final-installer.run | |||

try to run it by hand, same error about /tmp/tmp-something files. strange... | |||

notice it complains about "truncate", which truncate finds ~/bin/truncate, get rid of it, | |||

try again | |||

now complains about missing texinfo and zlib1g:i386 | |||

apt install texinfo -> ok | |||

apt install zlib1g:i386 -> installs bunch of gcc stuff -> ok | |||

try again | |||

reports "already installed" -> delete /opt/Xilinx/.xinstall/PetaLinux_2020.2/, delete entries in ~/.Xilinx/registry/installedSW.xml | |||

try again | |||

success | |||

</pre> | </pre> | ||

* | * install vivado 2022.1 and petalinux 2022.1 - everything is pretty much the same | ||

= | = Petalinux = | ||

* cd PetaLinux_GDM_CDM | |||

* petalinux-config | |||

* enable i2c MAC address and DHCP | |||

<pre> | <pre> | ||

git clone https://bitbucket.org:/team-ds-dm/ds-dm-u-boot-xlnx.git | |||

cd ds-dm-u-boot-xlnx | |||

git checkout ds-dm-u-boot-xlnx | |||

linux-components -> | |||

uboot -> ext-local-src | |||

external u-boot local source -> ds-dm-u-boot-xlnx (path to the customized uboot git repository) | |||

</pre> | |||

* enable DHCP | |||

<pre> | |||

Subsystem AUTO Hardware Settings -> Ethernet Settings | |||

randomize MAC address -> NO | |||

ethernet mac address -> leave empty | |||

obtain ip address automatically -> YES | |||

</pre> | |||

* set hostname and product names | |||

<pre> | |||

Firmware Version Configuration -> | |||

Host name -> "ds-dm" | |||

Product name -> "Petalinux_GDM_CDM" | |||

</pre> | |||

* configure linux kernel | |||

<pre> | |||

petalinux-config -c kernel | |||

</pre> | |||

* enable NFS-Root | |||

<pre> | |||

petalinux-config | |||

Image Packaging Configuration > Root File System Type -> set to NFS | |||

Location of NFS root directory set to "/nfsroot" | |||

// CDM SFP FIBER LINKS | petalinux-config -c kernel | ||

output reg [15:0] sfp_tx_data, | Networking support > IP: kernel level configuration | ||

output reg [1:0] | enable DHCP, BOOTP, RARP | ||

File systems > Network file systems > Root file systems on NFS | |||

</pre> | |||

* manually fix linux kernel command line: | |||

<pre> | |||

grep nfsroot PetaLinux_GDM_CDM/project-spec/configs/config | |||

edit CONFIG_SUBSYSTEM_BOOTARGS_GENERATED to read | |||

earlycon console=ttyPS0,115200 clk_ignore_unused panic=60 root=/dev/nfs nfsroot=/nfsroot/%s ip=dhcp rw | |||

</pre> | |||

* check configuration in | |||

** PetaLinux_GDM_CDM/project-spec/configs/config | |||

** PetaLinux_GDM_CDM/project-spec/configs/rootfs_config | |||

** PetaLinux_GDM_CDM/components/plnx_workspace/device-tree/device-tree/system-conf.dtsi | |||

= JTAG server = | |||

localhost:3121 | |||

= ds20k block = | |||

<pre> | |||

module ds20k | |||

( | |||

// CLOCK INPUTs | |||

input wire clk, | |||

input wire reset, // pulse for power-up reset | |||

input wire si5394_loln, // clock cleaner PLL is locked to selected input clock | |||

// REGISTER_DATA | |||

input wire [255:0] [31:0] register_data_in, | |||

output reg [255:0] [31:0] register_data_out, | |||

input wire register_we, | |||

input wire register_re, | |||

// GDM QSFP FIBER LINKS | |||

input wire qsfp_tx_data_ready, | |||

output reg [11:0] [15:0] qsfp_tx_data, | |||

output reg [11:0] [1:0] qsfp_tx_data_is_k, | |||

input wire [11:0] [15:0] qsfp_rx_data_error, // not sure what this is. | |||

input wire [11:0] [15:0] qsfp_rx_data, | |||

input wire [11:0] [1:0] qsfp_rx_data_is_k, | |||

// CDM SFP FIBER LINKS | |||

input wire sfp_tx_data_ready, | |||

output reg [15:0] sfp_tx_data, | |||

output reg [1:0] sfp_tx_data_is_k, | |||

input wire sfp_rx_data_error, // single bit indicating that RX link is up and data is good. | |||

input wire [15:0] sfp_rx_data, | input wire [15:0] sfp_rx_data, | ||

input wire [1:0] | input wire [1:0] sfp_rx_data_is_k, | ||

// VX_RXs | // VX_RXs | ||

input wire [3:0] | input wire [3:0] vx1_rx_async, | ||

input wire [3:0] | input wire [3:0] vx2_rx_async, | ||

input wire [3:0] | input wire [3:0] vx3_rx_async, | ||

input wire [3:0] | input wire [3:0] vx4_rx_async, | ||

input wire [3:0] | input wire [3:0] vx5_rx_async, | ||

input wire [3:0] | input wire [3:0] vx6_rx_async, | ||

input wire [3:0] | input wire [3:0] vx7_rx_async, | ||

input wire [3:0] | input wire [3:0] vx8_rx_async, | ||

input wire [3:0] | input wire [3:0] vx9_rx_async, | ||

input wire [3:0] | input wire [3:0] vx10_rx_async, | ||

input wire [3:0] | input wire [3:0] vx11_rx_async, | ||

input wire [3:0] | input wire [3:0] vx12_rx_async, | ||

// VX_TXs | // VX_TXs | ||

| Line 1,444: | Line 1,652: | ||

output reg [2:0] vx12_tx_out, | output reg [2:0] vx12_tx_out, | ||

// | // VX serial comunications | ||

input wire [11:0] vx_rx_ser_in, | |||

output reg [11:0] vx_tx_ser_out, | |||

// LEMO INPUTs | // LEMO INPUTs | ||

input wire [4:1] | input wire [4:1] ext_in_async, // direct connection to LEMO connectors, not clocked | ||

// LEMO OUTPUTs | // LEMO OUTPUTs | ||

| Line 1,455: | Line 1,664: | ||

// FRONT PANEL LEDs | // FRONT PANEL LEDs | ||

output reg [3:0] fp_led_out, // direct connection to LEMO connectors, not clocked | output reg [3:0] fp_led_out, // direct connection to LEMO connectors, not clocked | ||

); | ); | ||

</pre> | </pre> | ||

| Line 1,464: | Line 1,669: | ||

= world view = | = world view = | ||

Main components: | |||

* | * clock distribution - to ensure all digitizers run synchronously and waveform timestamp are easy to assemble intophysics events. | ||

* | * global trigger and run control - all digitizers are triggered at the same time to record calibration events, pulser events and the run startup synchronization sequence. | ||

* | * busy distribution - when some digitizers go busy and stop accepting triggers, physics events may become incomplete, this must be recorded and managed. | ||

* hitmap distribution - to create an online picture of the detector for monitoring and for triggering. | |||

== global clock distribution == | |||

== | Clock distribution ensures all digitizers run synchronously (on the same clock) and waveform timestamps are easy to assemble into physics events. The clock source is synchronized with GPS to ensure a metrologically validated clock frequency (tied to the SI definition of 1 second) and date stamp (via GPS IRIG-B date stamp). Individual digitizer waveform timestamp are reset at the begin of run to establish a valid time zero (run start time, date stamped with the GPS IRIG-B date stamp). | ||

Base clock is 125 MHz (8 ns). Individual digitizers are synchronized at initialization (power-up) time. Because of incontrollable delays in the electronics (i.e. variations between individual PLL chips in each digitizer), waveform timestamps between individual digitizers may be off by 1-2 clocks (8-16 ns). After the system is running and is stable (thermally and electrically), timestamp waveform variation and jitter are less than 1 ns. | |||

This is validated by feeding a common calibration pulser signal into analog inputs of each digitizer (at 100 Hz) and measuring (fitting) the pulse time in the waveform. With sufficient statistics, differences between waveform timestamp are measured with picosecond precision. | |||

CDM PLL allows fine phase adjustment of the 62.5 MHz VX2746 clock in groups of 6 clocks (2 groups per CDM) with precision 71.43 ps. | |||

Due to FPGA technology limitations (serial link hard IPs, PLLs, etc) the pattern of 1-2 clock delays between individual digitizers may change/shift from power up to power up. Significant additional work would be required to ensure this pattern is repeatable and stable after every power up and initialization. As mentioned before, after power up and initialization, variation between waveform timestamp is sub-nanosecond as measured by the analog calibration pulser. | |||

Clock chain: | |||

* GPS receiver (1pps clock reference and IRIG-B date stamp) | |||

* LNGS GPS clock distribution (fiber link to converter box at the experiment) | |||

* GPS 1pps to PRS-10 Rb atomic clock (10 MHz clock output) | |||

* 10 MHz clock from PRS-10 to GDM PLL (extra low jitter oscillator, 125 MHz clock output) | |||

* 125 MHz clock to GDM fiber link transmitters (2.5 Gbps line rate) | |||

* CDM fiber link receiver and clock recovery (125 MHz clock) | |||

* 125 MHz recovered clock to CDM PLL (extra low jitter oscillator, 62.5 MHz clock output) | |||

* 62.5 MHz CDM clock to VX2745 PLL via LVDS line | |||

* VX2745 PLL (125 MHz clock output) | |||

* 125 MHz clock to digitizer chips, clock counter and waveform timestamp. | |||

This is the normal mode of operation, with global clock synchronized with the GPS clock (metrologically referenced to SI 1 Hz definition). | |||

If GPS signal is not available, degraded modes of operation are available (in order of worsening performance) | |||

* PRS-10 Rb atomic clock synchronized with a battery-powered time-of-day chip | |||

* PRS-10 Rb atomic clock synchronized with Internet time (NTP) assuming Internet network connection is up | |||

* PRS-10 Rb clock standalone | |||

* GDM internal oscillator | |||

All degraded modes provide high precision low jitter 125 MHz system clock, but long term stability (seconds per day) will vary. (TBM) | |||

In the absence of GPS IRIG-B date stamp, the battery-powered time-of-day chip will be used (TBI) with fallback to Internet time (NTP). Date stamp long term stability is expected to be better than 1 second per day (TBI, TBM). | |||

Note: | |||

* TBM: to be measured | |||

* TBI: to be implemented | |||

Current status (April 2025): | |||

* full clock chain from GDM PLL to VX2745 digitizers is implemented and tested | |||

* waveform timestamp variations are measured (see report from Marek) | |||

* GDM external clock is validated (using VME-GRIFFIN-CDM high quality clock source module) | |||

* PRS-10 10 MHz and 1pps connection to GDM is implemented and tested | |||

* GPS receiver 1pps connection to PRS-10 is implemented and tested | |||

* GPS receiver IRIG-B date stamp connection to GDM tested using a software decoder. Hardware decoder and connection to time slice marker, TBI. | |||

* LNGS date stamp decoder and connection to time slice marker, TBI | |||

* LNGS 1pps connection to PRS-10, not available | |||

* operate vertical slize system from GPS, not available (GPS is in the det lab, vertical slice is in the daq lab). | |||

== global trigger distribution == | |||

Global trigger distribution provides a synchronous waveform trigger to all VX2745, all CDM and all VX2745 are provided wiht the same data and are all triggered at the same time (without accounting for the 1-2 clock offset described in the clock section). | |||

Global trigger is used for run control: the first trigger of a run resets the waveform timestamp counter, the CDM timestamp counter and the GDM timestamp counter. At the begin of run, GDM generates a sequence of triggers following an easy to identify pattern. If a VX2745 misses a trigger (for any reason), online and offline software can easily identify the tru run start time using this pattern. | |||

After a run has started, global trigger can be generated by a programmable pulser, by an external LEMO signal (i.e. external calibration signal, laser Q-switch, etc) and by the VX2745 trigger hitmap. | |||

Trigger sources (TRG): | |||

* TRG pulser | |||

* LEMO inputs | |||

* hitmap trigger | |||

Time slice marker sources (TSM): | |||

* TSM pulser | |||

Trigger chain, K-code and LVDS: | |||

* TRG/TSM source | |||

* TRG/TSM K-code from GDM to CDM | |||

* CDM K-code to LVDS line 12 and 13 lines (TRG and TSM) | |||

Latency from GDM LEMO input to CDM LVDS out: TBM | |||

Trigger chain, packet trigger: | |||

* GDM TRG/TSM source to TRG/TSM packet generator | |||

* or GDM hitmap group trigger packet generator | |||

* TRG/TSM packet from GDM to CDM | |||

* TRG/TSM packet from CDM to VX2745 via LVDS line, 62.5 MHz, 8b10b encoding. | |||

Latency from GDM LEMO input to VX2745 internal trigger: TBM | |||

Notes: | |||

TBM - to be measured | |||

TBI - to be implemented | |||

- | |||

Current status (Jan 2026): | |||

* LVDS TRG and TSM distribution is done and tested | |||

* packet TRG, TRIG48 and TSM distribution from GDM to CDM is done and tested | |||

* packet TRG, TRIG48 and TSM from CDM to VX2745 is done and tested | |||

* packet TRIG48 processing in the VX is done and tested | |||

== | == global busy distribution == | ||

If any VX2745 goes busy (for any reason) and stops accepting triggers, physics data may become incomplete. This situation needs to be recorded and managed. | |||

Busy chain: | |||

* VX2745 firmware busy logic (CAEN and Yair) generates the VX busy signal on LVDS line 9 (CDM VX_RX_2) | |||

* CDM monitors VX busy | |||

* CDM records busy transitions | |||

* CDM computes the "CDM busy" as grand-OR of all VX busy | |||

* CDM periodically transmits CDM busy status the GDM using special K-codes (NB: confirm transmission period) | |||

* GDM receives CDM busy updates and maintains "CDM busy" for each CDM | |||

* GDM records busy transitions | |||

* GDM computes "GDM busy" as grand-OR of all CDM busy | |||

* effectively, GDM busy is a grand-OR of all VX busy (with max delay, TBM) | |||

In the pilot implementation, any VX busy stops the experiment by sending a veto signal to all VX2745 which stops them from accepting triggers. | |||

Veto chain: | |||

* GDM computes "GDM veto" as GDM busy | |||

* GDM periodically transmits GDM veto status to all CDMs using special K-codes (NB: confirm transmission period) | |||

* CDM receive GDM veto updates and maintain the "CDM veto" signal | |||

* CDM computes "VX veto" as CDM veto | |||

* CDM transmits VX veto to all VX2745 on LVDS pair 13 | |||

* VX2745 firmware (Yair) has VX veto block all physics triggers (NB: except for the time slice marker?) | |||

Total delay from VX busy to VX veto (on the LVDS lines), TBM. | |||

* | Notes: | ||

* TBM - to be measured | |||

* TBI - to be implemented | |||

Current status (Jan 2026): | |||

* full busy chain from VX to CDM to GDM is implemented, tested | |||

* veto chain from GDM to CDM is implemented, tested | |||

* veto chain from CDM to LVDS pair 13 is implemented, tested | |||

* LVDS pair 13 veto inside the VX is implemented, tested | |||

* TRG switched from LVDS pair 12 to TRG packet, testing completed | |||

* TSM switched from LVDS pair 13 to TSM packet, testing completed | |||

* fine tuning of busy chain, VX buffer levels, etc, test in progress | |||

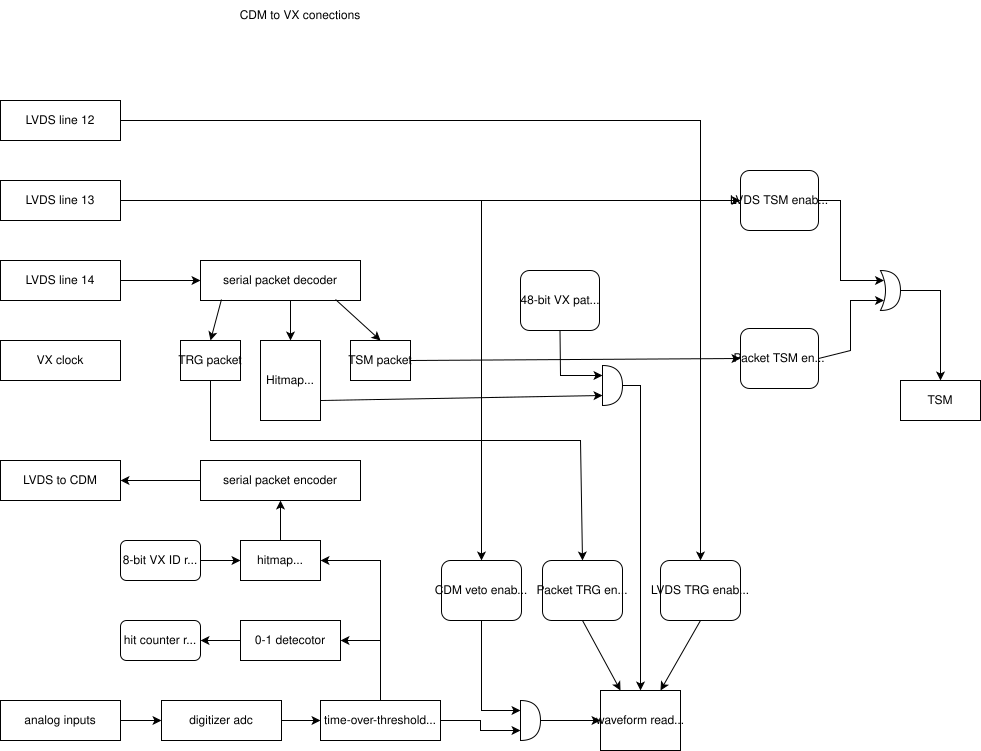

== vx hitmap and hitmap trigger == | |||

To monitor the system in real time and to generate group triggers, we use the VX hitmaps. | |||

Each VX2745 has 64 channels, each channel has a trigger logic block (digital discriminator) that generates a waveform self-trigger and sends a hitmap bit to the CDM (64-bits per VX2745) as a data packet. CDM passes hitmap data packets to the GDM and also records non-empty hitmap packets. CDM MIDAS frontend passes non-empty hitmap packets to MIDAS for online monitoring and visualization. GDM collects all the hitmaps and generates a global trigger. Alternatively, it generates a group trigger TRIG48 with a 48-bit bitmap indicating which VX2745 should trigger a waveform. | |||

Pilot implementation computes the hitmap trigger as a grand-OR of all hit maps. | |||

Hitmap chain: | |||

* VX2745 analog inputs to digitizers to digital trigger logic block, 1 bit per channel (CAEN, Yair) | |||

* 64-bits of hitmap (1 bit/channel) are collected and periodically transmitted to the CDM (Sam De Jong) (NB: confirm transmission period: see CDM page table "VX hit map" column "period", 0xD1 clocks is 1672 ns, should be reduced to 1500 ns, TBI) | |||

* VX hitmap packets are transmitted to the CDM on the LVDS line 10 (CDM VX_RX_1) at 62.5 MHz, 8b10b encoded. | |||

* CDM receives hitmap packets (12 input data streams, 12-to-1 packet mux) | |||

* CDM sends all hitmap packets to the GDM at 125 MHz, 16b20b encoded. | |||

* non-empty hitmap packets are written to the CDM-to-CPU data FIFO (and via MIDAS frontend to MIDAS SYSTEM event buffer) | |||

* grand-OR of VX hitmap packets (12*64 bits) can generate a CDM-local VX trigger | |||

* GDM receives hitmap packets, computes "GDM hitmap trigger" | |||

* if enabled, GDM hitmap trigger causes GDM trigger, which is processed as described in the global trigger section | |||

Delay, latency and jitter from analog pulse on the VX2745 analog input to VX trigger on LVDS line 12, TBM. | |||

TRIG48 VX group trigger: | |||

* GDM receives hitmap packets, computes the 48-bit bitmap of which VX2745 modules should trigger | |||

* how to specify this computation is not clear. a generic 12*64 MLU is impossible, insufficient RAM on the FPGA | |||

* 48-bit bitmap is sent to all CDMs as a TRIG48 data packet | |||

* CDM receives TRIG48 data packets from GDM and retransmits them to the VX2745 (all CDMs and all VXes see the same packets at the same time). | |||

* VX2745 receives the 48-bit trigger bitmap, compares it with it's own 48-bit bitmap if any common bits are set, triggers waveform readout of all channels (there will be no more than 48 VX2745 in the experiment) | |||

Pilot implementation of TRIG48 triggers on the CDM grand-or and generates a TRIG48 packet that contains a 48-bit bitmap stored in an AXI register. | |||

Example uses of TRIG48: | |||

* to trigger individual VX2745 modules: set the VX 48-bit map to the module number (vx05-0x1, vx06-0x2, vx07-0x4, etc), generate TRIG48 packet with a bitmap of VX modules that should trigger: 0xFFFF'FFFF'FFFF will trigger all modules, 0x1 will trigger only vx05, 0x2 will trigger only vx06, etc. (there is no more than 48 modules). | |||

* to trigger groups of VX2745 modules: set the bitmap of group 1 modules to 0x1, set the bitmap of group 2 modules to 0x2, generate TRIG48 packet with bitmap 0x0001 to trigger only group 1 modules, 0x0002 to trigger only group 2 modules, 0x3 to trigger both groups. | |||

Notes: | |||

* TBM - to be measured | |||

* TBI - to be implemented | |||

Current status (Jan 2026): | |||

* full chain (VX analog input to hitmap generator to CDM to GDM) is implemented, testing in progress | |||

* GDM grand-or trigger is implemented | |||

* VX hitmap packet generator, testing in progress (Yair firmware) | |||

* CDM hitmap processing, implemented, tested | |||

* GDM hitmap processing, implemented, tested | |||

* pilot TRIG48 trigger generator in GDM, CDM, tested | |||

* TRIG48 trigger in VX, implemented, tested | |||

* MIDAS frontend readout of hitmap data from FPGA FIFO: implemented, testing in progress (FIFO code: Ian, done; integration and C++ code: KO) | |||

* online monitoring and visualization in MIDAS: TBI | |||

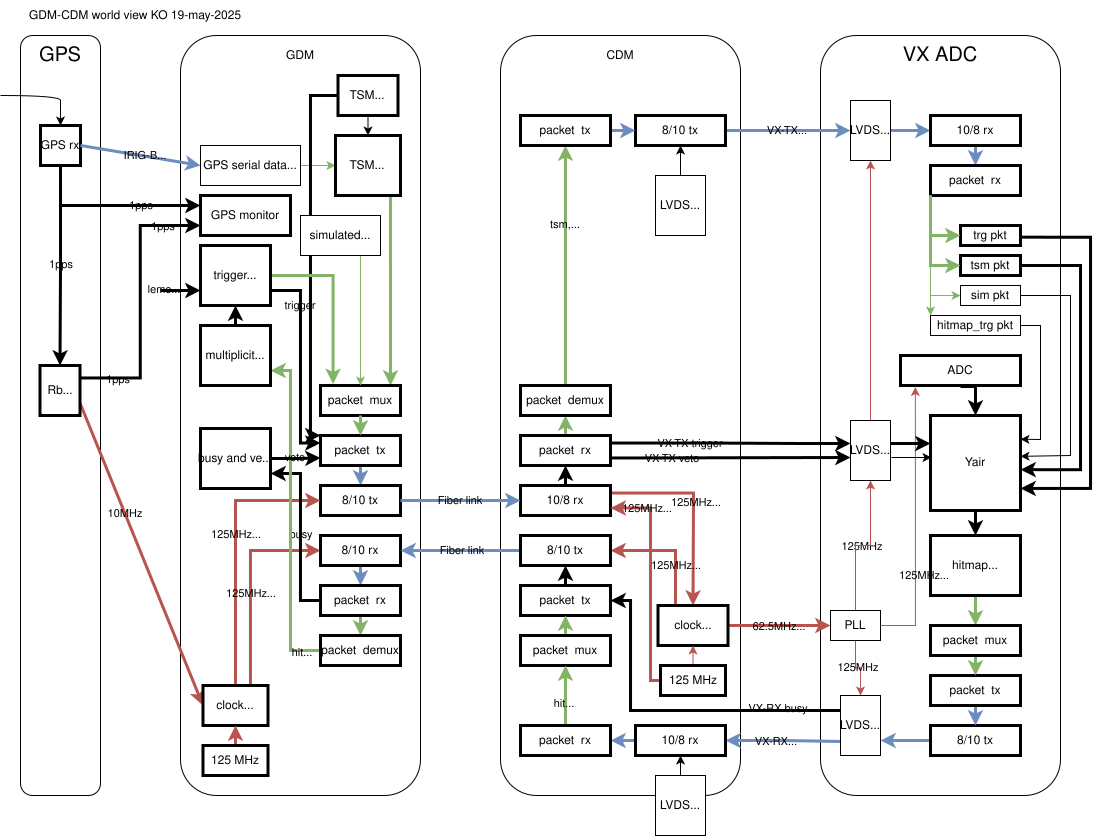

== firmware map == | |||

Note: | |||

* red lines: clocks | |||

* green lines: AXI/Avalon packet streams | |||

* blue lines: serial data | |||

[[File:GDM-CDM-VX.drawio.svg]] | |||

== description == | |||

same thing, in words: | |||

<pre> | <pre> | ||

detector | |||

digitizer, 125 MHz | |||

digital filter | |||

digital discriminator | |||

hit map, 64 bits at 125 MHz (could be 250 MHz, filter and discriminator clock) | |||

packetizer, 64 bits -> id, timestamp, 8x 8-bit words, eop | |||

8/10 serializer, 12.5 MHz parallel in, 125 MHz serial out | |||

lvds line to CDM vx_rx | |||

BBB: also VX busy to lvds line to CDM vx_rx, do not want to depend on serial comm for vx busy, do not want to inject async data into the hit map packet stream | |||

--- CDM | |||

lvds line capture in IBUF register, vxN_rx clock, 125 MHz clock, from PLL with adjustable phase, scan phase to find sweet spot | |||

vx rx 10/8 deserializer, vxN_rx clock, stobes out parallel data every 10 clocks at 12.5 MHz | |||

vx rx phase transfer from vxN_rx clock to main CDM clock, have 10 clocks for transfer to happen | |||

from here everything is on the CDM main clock | |||

vx rx packet adapter, 12.5 MHz 8-bit packets to 125 MHz 16-bit packets, internal FIFO to avoid data overrun | |||

sfp tx mux, all VX packet streams into one CDM sfp tx packet stream | |||

BBB: capture VX RX busy to CDM main clock (IBUF register), grand-or becomes vx_rx_busy | |||

sfp tx packetizer (data,eop,vx_rx_busy -> data,k) | |||

sfp tx 16/20 serializer, 16 bit at 125 MHz in, 2500 MHz serial out (20 bits at 125 MHz) | |||

sfp tx fiber link to GDM, 2 Gigabits/sec | |||

--- GDM | |||

qsfp rx deserializer, 16 bit at 125 MHz output on main GDM clock | |||

qsfp rx depacketizer (data,k -> packet data,eop; qsfp_rx_busy) | |||

qsfp rx demux, hit map packets routed to GDM trigger logic block | |||

GDM trigger logic block looks at hit map, generates yes/no trigger decision, encodes it as a trigger packet | |||

TSM generator encodes GPS time data as a TSM packet | |||

qsfp tx mux - trigger packets, tsm packets, etc to qsfp tx packet stream | |||

qsfp tx packetizer (data,eop;trg,tsm,bsy -> data,k) | |||