Cdms workshop: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

|||

| Line 4: | Line 4: | ||

[[Image:Midas_intro-04.png|MIDAS general picture]] | [[Image:Midas_intro-04.png|MIDAS general picture]] | ||

== MIDAS main data path == | == MIDAS main data path == | ||

| Line 22: | Line 17: | ||

Needs to scale from 0.5GB/0.3GHz/1core PPC on FPGA to 1GB/1GHz/1core 32-bit ARM to 64GB/4GHz/12core 64-bit x86! | Needs to scale from 0.5GB/0.3GHz/1core PPC on FPGA to 1GB/1GHz/1core 32-bit ARM to 64GB/4GHz/12core 64-bit x86! | ||

== MIDAS web security == | |||

[[Image:web_security_svg.svg]] | |||

[[Image:web_security.png]] | |||

== MIDAS slow controls paths == | == MIDAS slow controls paths == | ||

Revision as of 08:36, 10 March 2014

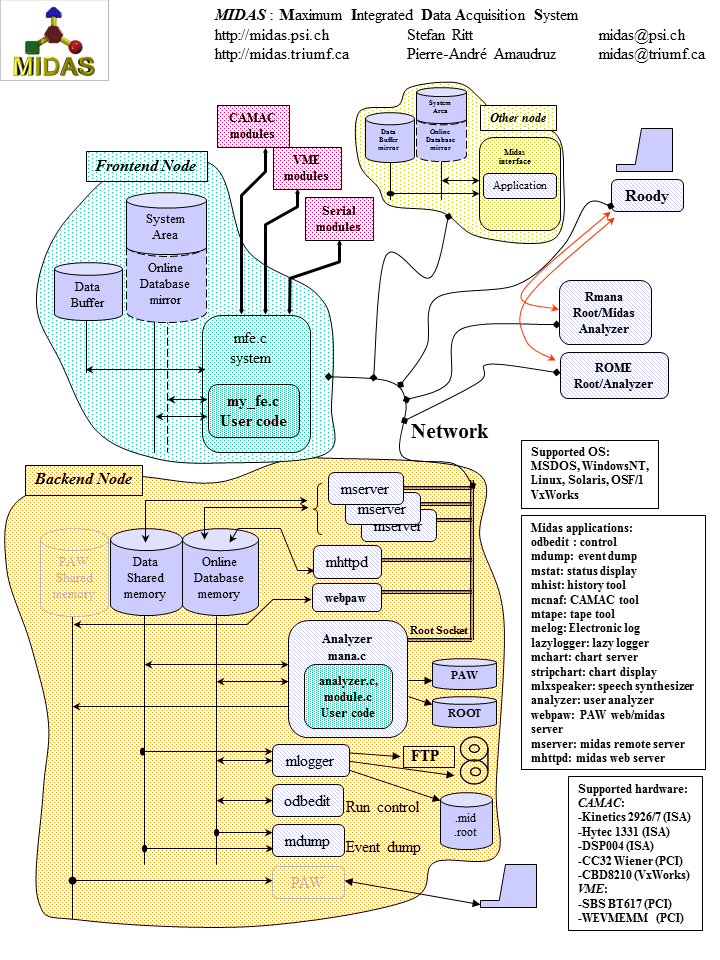

Notes for the CDMS workshop March 2014

MIDAS general picture

MIDAS main data path

hardware -> mfe user thread -> ring buffer -> (compression thread -> ring buffer ->) mfe main thread -> TCP socket -> mserver -> event buffer -> event builder thread -> SYSTEM buffer -> mlogger -> (ring buffer -> compression thread -> ) data file -> lazylogger -> dcache/castor/hadoop/cloud storage

Needs to scale from 0.5GB/0.3GHz/1core PPC on FPGA to 1GB/1GHz/1core 32-bit ARM to 64GB/4GHz/12core 64-bit x86!

MIDAS web security

Error creating thumbnail: convert-im6.q16: non-conforming drawing primitive definition `stroke-linecap' @ error/draw.c/RenderMVGContent/4404.

MIDAS slow controls paths

TBW

MIDAS history paths

TBW