VME-CDM: Difference between revisions

| (33 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

= VME-CDM - GRIFFIN Clock Distribution Module = | |||

= References = | |||

* edev login: no public access, sorry! | * edev login: no public access, sorry! | ||

| Line 7: | Line 7: | ||

* ladd00 svn login: username: svn, password: svn | * ladd00 svn login: username: svn, password: svn | ||

* [http://edev.triumf.ca/projects/edevel00163] VME-CDM project page on edev.triumf.ca | * (dead) [http://edev.triumf.ca/projects/edevel00163] VME-CDM project page on edev.triumf.ca | ||

* [https://edev.triumf.ca/projects/edevel00163/repository/entry/tags/Rev2/Altium/VME%20-%20Clock%20Distribution%20Module.pdf] Rev2 board schematics (link to edev) | * (dead) [https://edev.triumf.ca/projects/edevel00163/repository/entry/tags/Rev2/Altium/VME%20-%20Clock%20Distribution%20Module.pdf] Rev2 board schematics (link to edev) | ||

* [https://edev-group.triumf.ca/hw/vme/cdm] VME-CDM project page on edev gitlab | * [https://edev-group.triumf.ca/hw/vme/cdm] VME-CDM project page on edev gitlab | ||

* [https://github.com/EmcraftSystems/linux-emcraft] Microsemi ARM processor linux software | * [https://github.com/EmcraftSystems/linux-emcraft] Emcraft Microsemi ARM processor linux software | ||

=== General characteristics | = VME-CDM-Rev3 = | ||

* Manual: [[File:Clock Distribution Module Rev 3 - User Mannual.pdf]] | |||

* Schematics: [[File:VME - Clock Distribution Module.pdf]] | |||

= VME-CDM-Rev2 = | |||

= General characteristics = | |||

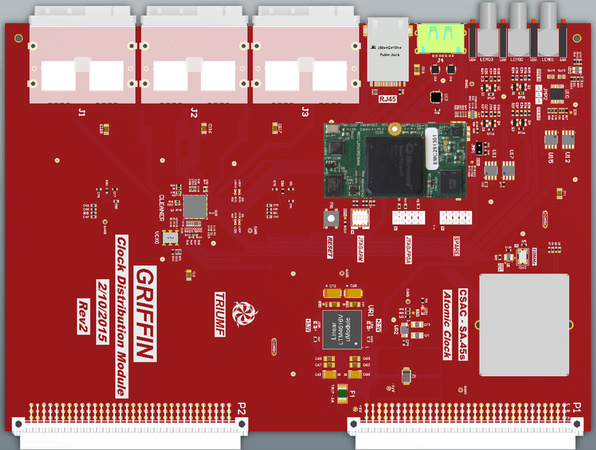

==== Photos ==== | ==== Photos ==== | ||

[[Image: | [[Image:VME_-_Clock_Distribution_Module_-_3D_Top_Assembly_Thumbnail.jpg]] | ||

==== Board schematics ==== | ==== Board schematics ==== | ||

[[VME_- | [[Media:VME_-_Clock_Distribution_Module_Rev2.pdf]] | ||

==== Available hardware ==== | ==== Available hardware ==== | ||

* LMK04821 PLL/clock cleaner | * LMK04821 PLL/clock cleaner. Manual: [[Media:Snas605ar-LMK04821.pdf]] | ||

* Socket for Atomic clock CSAC Symmetricom CSAC-SA.45s | * Socket for Atomic clock CSAC Symmetricom CSAC-SA.45s | ||

* Microsemi Smartfusion2 SoC M2S-FG484 (ARM CPU) | * Microsemi Smartfusion2 SoC M2S-FG484 (ARM CPU). Product page: https://www.emcraft.com/products/255 | ||

* 10/100 Mbit/s ethernet | * 10/100 Mbit/s ethernet | ||

* no VME interface | * no VME interface | ||

| Line 42: | Line 48: | ||

** LEMO3B - 10MHz_OUT_NIM | ** LEMO3B - 10MHz_OUT_NIM | ||

* 4 red and 4 green LEDs | * 4 red and 4 green LEDs | ||

=== ARM processor === | |||

==== Console connection ==== | |||

* use a USB type-A to type-A cable to connect from CDM eSATA connector to computer USB connector. | |||

* on linux, two /dev/ttyUSB ports will show up (FTDI USB-serial chip) | |||

* use minicom (or other tool) to connect with these serial port settings: | |||

<pre> | |||

Serial Device : /dev/ttyUSB2 | |||

Bps/Par/Bits : 115200 8N1 | |||

Hardware Flow Control : No | |||

Software Flow Control : No | |||

</pre> | |||

* type "enter" several times to get the "#" root shell prompt | |||

* on power cycle, observe the output from u-boot and from the linux kernel https://daqshare.triumf.ca/~olchansk/VME-CDM/cdm-boot.txt | |||

* press "enter" or "space" to break into the u-boot command line | |||

* original u-boot settings from Bryerton are here https://daqshare.triumf.ca/~olchansk/VME-CDM/cdm-uboot-printenv.txt | |||

==== Useful u-boot commands ==== | |||

* reset - reboot the CPU | |||

* printenv - print environment | |||

* saveenv - save environment | |||

* run update - load new firmware image to write it to onboard flash. For it to work: | |||

** IP address settings have to be correct | |||

** tftpd should be configured on the boot server | |||

** developer.uImage should be placed in /var/lib/tftpboot on the boot server | |||

** if successful, the command will print hashes "#" as data is loaded via tftp and finally report successful write to SPI flash | |||

<pre> | |||

# reboot | |||

### press <enter> many times until you get into the u-boot prompt | |||

run update | |||

reset | |||

</pre> | |||

* boot linux kernel with DHCP network configuration: | |||

<pre> | |||

setenv addip setenv bootargs m2s_platform=m2s-fg484-som console=ttyS0,115200 panic=10 ip=dhcp | |||

saveenv | |||

reset | |||

</pre> | |||

==== Building the linux kernel and userland ==== | |||

The linux kernel image developer.uImage contains the linux kernel fused | |||

with the root filesystem. There is no separate initramfs file, there | |||

is no separate root filesystem in flash, there is no nfs-root filesystem | |||

on the boot server. | |||

To build the image do this: | |||

<pre> | |||

ssh agdaq@alphagdaq | |||

cd /home/agdaq/online/firmware/cdm/emcraft/ | |||

. ./ACTIVATE.sh | |||

cd projects/developer | |||

make MCU=M2S INSTALL_ROOT=$PWD/../.. | |||

# developer.uImage will be built | |||

as root: cp /home/agdaq/online/firmware/cdm/emcraft/projects/developer/developer.uImage /var/lib/tftpboot/ | |||

</pre> | |||

To customize the linux kernel, edit developer.kernel.M2S (this is a regular linux .config file). "make" will copy it into the linux kernel source tree (overwriting the .config file already there). | |||

To customize the root filesystem, edit developer.initramfs and edit files in "local": | |||

* local/rc --- is the command file executed after the linux kernel is booted (mount filesystems, setup GPIO, etc) | |||

* local/authorized_keys --- is the ssh key file for login into root@cdm01 | |||

==== Controlling the clock cleaner PLL ==== | |||

the clock cleaner PLL is controlled by the program griffin_cdm in emcraft/projects/developer/griffin_cdm | |||

=== FPGA === | |||

Nothing is known about the FPGA. It probably needs to be programmed with something | |||

to route the ARM processor GPIOs to the correct chip I/O pins. | |||

=== Board controls === | |||

The CDM board is controlled by these GPIOs: | |||

* SEL_NIM_TTL - LEMO inputs TTL or NIM - pin67 (MSIO47NB1) - gpio3 | |||

* EXT_ESATA_SYNC_SEL - sync signal is from LEMO or from eSATA - pin14 (DDRIO151NB5) - gpio5 | |||

* 10MHz_SOURCE_SEL - PLL clk0 clock is 10MHz oscillator or CSAC atomic clock - pin79 (MSIO0PB3) - gpio4 | |||

* 6 enables for CLK0-3, 4-7, 8-11, 12-15, 16-19 and 20-23 - pins 46,48,50,52,54,56 - (MSIOD123NB7 & co) - gpio6..11 | |||

* 8 LEDs (alternating red and green) - FP_LED1..8 - gpio24..31 | |||

* LMK_SYNC - pin64 (SPI1_nSS1) - gpio12 | |||

* probably LMK_StatusLD1 and LMK_StatusLD2 - pins66 and 68 (SPI1_nSS2 and SPI1_nSS3) - gpio1 and gpio2 | |||

=== VME-CDM-Rev3 Port mapping === | |||

<pre> | |||

| | |||

| LEMO1A | LEMO1B | |||

| | |||

| LEMO2A | LEMO2B | |||

| | |||

| LEMO3A | LEMO3B | |||

| | |||

| eSATA | |||

| | |||

| ETH | |||

| | |||

| MiniSAS-1 | |||

| | |||

| MiniSAS-2 | |||

| | |||

| MiniSAS-3 ---> index 0 | |||

| | |||

| MiniSAS-4 | |||

| | |||

| MiniSAS-5 | |||

| | |||

| MiniSAS-6 | |||

| | |||

</pre> | |||

Latest revision as of 02:49, 10 September 2021

VME-CDM - GRIFFIN Clock Distribution Module

References

- edev login: no public access, sorry!

- edev-pps login: no public access, sorry!

- ladd00 svn login: username: svn, password: svn

- (dead) [1] VME-CDM project page on edev.triumf.ca

- (dead) [2] Rev2 board schematics (link to edev)

- [3] VME-CDM project page on edev gitlab

- [4] Emcraft Microsemi ARM processor linux software

VME-CDM-Rev3

- Manual: File:Clock Distribution Module Rev 3 - User Mannual.pdf

- Schematics: File:VME - Clock Distribution Module.pdf

VME-CDM-Rev2

General characteristics

Photos

Board schematics

Media:VME_-_Clock_Distribution_Module_Rev2.pdf

Available hardware

- LMK04821 PLL/clock cleaner. Manual: Media:Snas605ar-LMK04821.pdf

- Socket for Atomic clock CSAC Symmetricom CSAC-SA.45s

- Microsemi Smartfusion2 SoC M2S-FG484 (ARM CPU). Product page: https://www.emcraft.com/products/255

- 10/100 Mbit/s ethernet

- no VME interface

- dual mode eSATA connector:

- eSATA clock+sync input or

- USB-A access to ARM CPU serial console via FTDI USB-serial chip

- 24 clock+sync outputs (LVDS) via 6 mini-SAS connectors (SFF-8088)

- 3 dual LEMO connectors: (from top to bottom) ("A" is left, "B" ir right)

- LEMO1A - EXT_SYNC_IN (NIM or TTL sync)

- LEMO1B - EXT_RefClk_IN (NIM or TTL clock)

- LEMO2A - CLOCK_OUT1_NIM (LVDS_CLK7)

- LEMO2B - selected by jumper: CLOCK_OUT2_NIM (LVDS_CLK6) or GPS_1PPS_IN

- LEMO3A - 1PPS_OUT_NIM

- LEMO3B - 10MHz_OUT_NIM

- 4 red and 4 green LEDs

ARM processor

Console connection

- use a USB type-A to type-A cable to connect from CDM eSATA connector to computer USB connector.

- on linux, two /dev/ttyUSB ports will show up (FTDI USB-serial chip)

- use minicom (or other tool) to connect with these serial port settings:

Serial Device : /dev/ttyUSB2 Bps/Par/Bits : 115200 8N1 Hardware Flow Control : No Software Flow Control : No

- type "enter" several times to get the "#" root shell prompt

- on power cycle, observe the output from u-boot and from the linux kernel https://daqshare.triumf.ca/~olchansk/VME-CDM/cdm-boot.txt

- press "enter" or "space" to break into the u-boot command line

- original u-boot settings from Bryerton are here https://daqshare.triumf.ca/~olchansk/VME-CDM/cdm-uboot-printenv.txt

Useful u-boot commands

- reset - reboot the CPU

- printenv - print environment

- saveenv - save environment

- run update - load new firmware image to write it to onboard flash. For it to work:

- IP address settings have to be correct

- tftpd should be configured on the boot server

- developer.uImage should be placed in /var/lib/tftpboot on the boot server

- if successful, the command will print hashes "#" as data is loaded via tftp and finally report successful write to SPI flash

# reboot ### press <enter> many times until you get into the u-boot prompt run update reset

- boot linux kernel with DHCP network configuration:

setenv addip setenv bootargs m2s_platform=m2s-fg484-som console=ttyS0,115200 panic=10 ip=dhcp saveenv reset

Building the linux kernel and userland

The linux kernel image developer.uImage contains the linux kernel fused with the root filesystem. There is no separate initramfs file, there is no separate root filesystem in flash, there is no nfs-root filesystem on the boot server.

To build the image do this:

ssh agdaq@alphagdaq cd /home/agdaq/online/firmware/cdm/emcraft/ . ./ACTIVATE.sh cd projects/developer make MCU=M2S INSTALL_ROOT=$PWD/../.. # developer.uImage will be built as root: cp /home/agdaq/online/firmware/cdm/emcraft/projects/developer/developer.uImage /var/lib/tftpboot/

To customize the linux kernel, edit developer.kernel.M2S (this is a regular linux .config file). "make" will copy it into the linux kernel source tree (overwriting the .config file already there).

To customize the root filesystem, edit developer.initramfs and edit files in "local":

- local/rc --- is the command file executed after the linux kernel is booted (mount filesystems, setup GPIO, etc)

- local/authorized_keys --- is the ssh key file for login into root@cdm01

Controlling the clock cleaner PLL

the clock cleaner PLL is controlled by the program griffin_cdm in emcraft/projects/developer/griffin_cdm

FPGA

Nothing is known about the FPGA. It probably needs to be programmed with something to route the ARM processor GPIOs to the correct chip I/O pins.

Board controls

The CDM board is controlled by these GPIOs:

- SEL_NIM_TTL - LEMO inputs TTL or NIM - pin67 (MSIO47NB1) - gpio3

- EXT_ESATA_SYNC_SEL - sync signal is from LEMO or from eSATA - pin14 (DDRIO151NB5) - gpio5

- 10MHz_SOURCE_SEL - PLL clk0 clock is 10MHz oscillator or CSAC atomic clock - pin79 (MSIO0PB3) - gpio4

- 6 enables for CLK0-3, 4-7, 8-11, 12-15, 16-19 and 20-23 - pins 46,48,50,52,54,56 - (MSIOD123NB7 & co) - gpio6..11

- 8 LEDs (alternating red and green) - FP_LED1..8 - gpio24..31

- LMK_SYNC - pin64 (SPI1_nSS1) - gpio12

- probably LMK_StatusLD1 and LMK_StatusLD2 - pins66 and 68 (SPI1_nSS2 and SPI1_nSS3) - gpio1 and gpio2

VME-CDM-Rev3 Port mapping

| | LEMO1A | LEMO1B | | LEMO2A | LEMO2B | | LEMO3A | LEMO3B | | eSATA | | ETH | | MiniSAS-1 | | MiniSAS-2 | | MiniSAS-3 ---> index 0 | | MiniSAS-4 | | MiniSAS-5 | | MiniSAS-6 |