BNMR: Helicity: Difference between revisions

mNo edit summary |

No edit summary |

||

| Line 9: | Line 9: | ||

== Introduction == | == Introduction == | ||

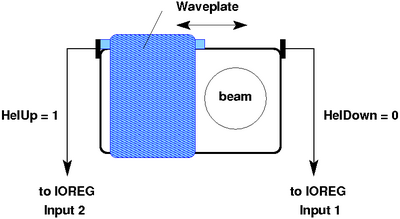

The {{bnmqr|join=and}} experiments control the helicity via the PPG "POL DRV" output. The helicity is changed using a waveplate (Figure 1) that is moved into and out of the beam. The two helicity states are called "UP" and "DOWN". An experimental parameter ''flip helicity'' is provided for each [[BNMR#Experimental (PPG) Modes|Experimental Mode]]. When this is set to true, the helicity will be flipped. Some modes flip the helicity after each PPG cycle, others at the end of the scan. | The {{bnmqr|join=and}} experiments control the helicity via the PPG "POL DRV" output. The helicity is changed using a waveplate (Figure 1) that is moved into and out of the beam. The two helicity states are called "UP" and "DOWN". An experimental parameter ''flip helicity'' is provided for each [[BNMR#Experimental (PPG) Modes|Experimental Mode]]. When this is set to true, the helicity will be flipped. Some modes flip the helicity after each PPG cycle, others at the end of the scan. | ||

* In [[BNMR Dual Channel Mode|dual channel mode]], both {{bnmqr|join=and}} may have helicity flipping enabled. | |||

* If [[BNMR Dual Channel Mode#Single_Channel_Mode|single channel mode]] at least one system must have helicity flipping disabled, to avoid the experiments fighting each other. | |||

[[Image:waveplate.png|400px|center|]] | [[Image:waveplate.png|400px|center|]] | ||

<br clear=all> | <br clear=all> | ||

| Line 16: | Line 20: | ||

</center> | </center> | ||

== Helicity | == Helicity switch box == | ||

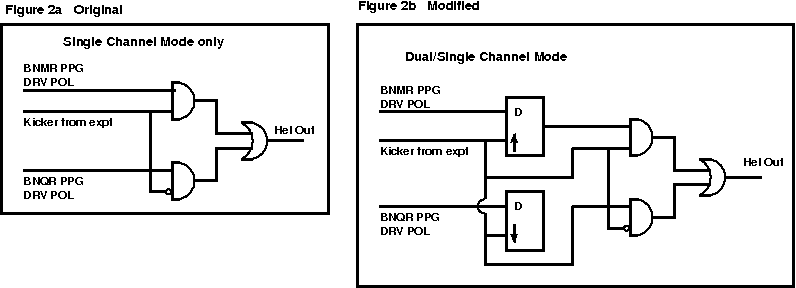

Since both experiments {{bnmqr|join=and}} control the same hardware (the helicity plate), signals to drive the helicity from both experiments are connected to a helicity switch box (Rolf's box), Figure 2. These signals are from each experiment's PPG "POL DRV" output. The electronics is edge-driven, so it only changes when it sees an edge. To ensure a particular helicity state at the begin-of-run in single channel mode (e.g. DOWN), the PPG must drive the helicity DOWN-UP-DOWN. In dual channel mode, it is not possible to ensure the required helicity in the way at the begin of run. It is assumed that by the second PPG cycle, the helicity will be in the correct state and the latched helicity readback provides confirmation. The first cycle is always discarded. | Since both experiments {{bnmqr|join=and}} control the same hardware (the helicity plate), signals to drive the helicity from both experiments are connected to a helicity switch box (Rolf's box), Figure 2. These signals are from each experiment's PPG "POL DRV" output. The electronics is edge-driven, so it only changes when it sees an edge. To ensure a particular helicity state at the begin-of-run in single channel mode (e.g. DOWN), the PPG must drive the helicity DOWN-UP-DOWN. In dual channel mode, it is not possible to ensure the required helicity in the way at the begin of run. It is assumed that by the second PPG cycle, the helicity will be in the correct state and the latched helicity readback provides confirmation. The first cycle is always discarded. | ||

The experiment requests the helicity state for its next cycle by setting the PPG "POL DRV" output. In single channel mode, the helicity state is changed immediately. In dual channel mode, the helicity is not changed until that experiment receives the beam (see [[BNMR Dual Channel Mode#Helicity]]). A circuit diagram of the helicity switch box as used for single and dual channel modes is shown in Figure 2b. (Figure 2a shows the original, single channel mode only). The D-type flip flops are edge driven, so they only change when an edge from the beam kicker signal is received. | The experiment requests the helicity state for its next cycle by setting the PPG "POL DRV" output. In single channel mode, the helicity state is changed immediately. In dual channel mode, the helicity is not changed until that experiment receives the beam (see [[BNMR Dual Channel Mode#Helicity]]). A circuit diagram of the helicity switch box as used for single and dual channel modes is shown in Figure 2b. (Figure 2a shows the original, single channel mode only). The D-type flip flops are edge driven, so they only change when an edge from the beam kicker signal is received. | ||

The EPICS Helicity switch <code>ILE2:POLSW2:STATLOC</code> must be set to <code>DAQ</code> control if helicity flipping is enabled. If helicity flipping is disabled, the switch can be set for either DAQ or EPICS control. | |||

[[Image:helicity_switch_box.png|center|frame|Figure 2 Helicity Switch box]] | [[Image:helicity_switch_box.png|center|frame|Figure 2 Helicity Switch box]] | ||

<br clear=all> | <br clear=all> | ||

== Helicity | == Helicity readback == | ||

Helicity | Helicity readback signals have been provided in recent years (Figure 1) so that the state of the helicity can be read with certainty, particularly in dual channel mode. The helicity state is read using a VME NIMIO32 register specially modified for the {{bnmqr|join=and}} experiments (see [[BNMR: DAQ Hardware Connections#NIMIO32|NIMIO32]] for details). Each experiment in provided with a VMEIO32 register. | ||

It provides a helicity readout for the present state of the helicity (used in single channel mode) as well as a latched helicity readout for dual channel mode. The latched readout latches the helicity state at the time that channel (BNMR or BNQR) has the beam. | It provides a helicity readout for the present state of the helicity (used in single channel mode) as well as a latched helicity readout for dual channel mode. The latched readout latches the helicity state at the time that channel (BNMR or BNQR) has the beam. | ||

== Helicity test program == | == Helicity test program == | ||

There is a helicity test program on both experiments | There is a MIMIO32/helicity test program on both experiments - see [[BNMR:_Hardware_Debugging#NIMIO32_.2F_beam_simulator|the hardware debugging page]]. | ||

== Helicity sleep time == | |||

After the helicity is flipped, experimenters usually want to wait a certain time before the next PPG cycle. This time is the helicity sleep time. In [[BNMR Dual Channel Mode#Single Channel Mode|single channel mode]], the helicity sleep time parameter can be found with the other experimental parameters on the [[BNMR: Custom Settings page|Settings page]]. | |||

In [[BNMR Dual Channel Mode|dual channel mode]], the helicity sleep time is programmed by the experimenters in the timing of the EPICS switching between channels, and the ODB parameter is ignored. | |||

== EPICS helicity checks == | |||

= | The ODB parameter {{Odbpath|path=/Scanning/Helicity/Settings/Enable checks}} causes the frontend program to perform the following checks: | ||

* If helicity flipping is enabled | |||

** Verifies that the EPICS Helicity switch <code>ILE2:POLSW2:STATLOC</code> is set to DAQ control at the start of the run | |||

** In [[BNMR Dual Channel Mode#Single Channel Mode|single channel mode]] | |||

*** at the start of run the program will attempt to set the helicity to the initial state (HEL_DOWN) and check the read back | |||

*** after each helicity flip, the program will check the Helicity state using the [[#Helicity Read Back|Helicity read back]] values. | |||

** in [[BNMR Dual Channel Mode|dual channel mode]] | |||

*** after each helicity flip, after each cycle the program will check the Helicity state using the [[#Helicity Read Back|Helicity read-back]] latched values. | |||

* | * If helicity flipping is disabled | ||

** Verifies that the EPICS Helicity switch <code>ILE2:POLSW2:STATLOC</code> is set to EPICS control at the start of the run | |||

< | |||

</ | |||

* In [[BNMR Dual Channel Mode#Single Channel Mode|single channel mode]] | |||

** at the start of run the program will attempt to set the helicity to the initial state (HEL_DOWN) and check the read back | |||

** after each helicity flip, the program will check the Helicity state using the [[#Helicity Read Back|Helicity read back]] values. | |||

* in [[BNMR Dual Channel Mode|dual channel mode]] | |||

** after each helicity flip, after each cycle the program will check the Helicity state using the [[#Helicity Read Back|Helicity read-back]] latched values. | |||

If the readback does not match the set value, the cycle will be skipped and the program will try once more to set the required helicity state. | If the readback does not match the set value, the cycle will be skipped and the program will try once more to set the required helicity state. | ||

[[Category:BNMR]] [[Category:Dual Channel Mode]] [[Category:Hardware]] | [[Category:BNMR]] [[Category:Dual Channel Mode]] [[Category:Hardware]] | ||

Revision as of 23:07, 27 April 2022

Links

Introduction

The bnmr and bnqr experiments control the helicity via the PPG "POL DRV" output. The helicity is changed using a waveplate (Figure 1) that is moved into and out of the beam. The two helicity states are called "UP" and "DOWN". An experimental parameter flip helicity is provided for each Experimental Mode. When this is set to true, the helicity will be flipped. Some modes flip the helicity after each PPG cycle, others at the end of the scan.

- In dual channel mode, both bnmr and bnqr may have helicity flipping enabled.

- If single channel mode at least one system must have helicity flipping disabled, to avoid the experiments fighting each other.

Figure 1 Helicity Waveplate

Helicity switch box

Since both experiments bnmr and bnqr control the same hardware (the helicity plate), signals to drive the helicity from both experiments are connected to a helicity switch box (Rolf's box), Figure 2. These signals are from each experiment's PPG "POL DRV" output. The electronics is edge-driven, so it only changes when it sees an edge. To ensure a particular helicity state at the begin-of-run in single channel mode (e.g. DOWN), the PPG must drive the helicity DOWN-UP-DOWN. In dual channel mode, it is not possible to ensure the required helicity in the way at the begin of run. It is assumed that by the second PPG cycle, the helicity will be in the correct state and the latched helicity readback provides confirmation. The first cycle is always discarded.

The experiment requests the helicity state for its next cycle by setting the PPG "POL DRV" output. In single channel mode, the helicity state is changed immediately. In dual channel mode, the helicity is not changed until that experiment receives the beam (see BNMR Dual Channel Mode#Helicity). A circuit diagram of the helicity switch box as used for single and dual channel modes is shown in Figure 2b. (Figure 2a shows the original, single channel mode only). The D-type flip flops are edge driven, so they only change when an edge from the beam kicker signal is received.

The EPICS Helicity switch ILE2:POLSW2:STATLOC must be set to DAQ control if helicity flipping is enabled. If helicity flipping is disabled, the switch can be set for either DAQ or EPICS control.

Helicity readback

Helicity readback signals have been provided in recent years (Figure 1) so that the state of the helicity can be read with certainty, particularly in dual channel mode. The helicity state is read using a VME NIMIO32 register specially modified for the bnmr and bnqr experiments (see NIMIO32 for details). Each experiment in provided with a VMEIO32 register. It provides a helicity readout for the present state of the helicity (used in single channel mode) as well as a latched helicity readout for dual channel mode. The latched readout latches the helicity state at the time that channel (BNMR or BNQR) has the beam.

Helicity test program

There is a MIMIO32/helicity test program on both experiments - see the hardware debugging page.

Helicity sleep time

After the helicity is flipped, experimenters usually want to wait a certain time before the next PPG cycle. This time is the helicity sleep time. In single channel mode, the helicity sleep time parameter can be found with the other experimental parameters on the Settings page.

In dual channel mode, the helicity sleep time is programmed by the experimenters in the timing of the EPICS switching between channels, and the ODB parameter is ignored.

EPICS helicity checks

The ODB parameter /Scanning/Helicity/Settings/Enable checks causes the frontend program to perform the following checks:

- If helicity flipping is enabled

- Verifies that the EPICS Helicity switch

ILE2:POLSW2:STATLOCis set to DAQ control at the start of the run - In single channel mode

- at the start of run the program will attempt to set the helicity to the initial state (HEL_DOWN) and check the read back

- after each helicity flip, the program will check the Helicity state using the Helicity read back values.

- in dual channel mode

- after each helicity flip, after each cycle the program will check the Helicity state using the Helicity read-back latched values.

- Verifies that the EPICS Helicity switch

- If helicity flipping is disabled

- Verifies that the EPICS Helicity switch

ILE2:POLSW2:STATLOCis set to EPICS control at the start of the run

- Verifies that the EPICS Helicity switch

If the readback does not match the set value, the cycle will be skipped and the program will try once more to set the required helicity state.