DarkLight: Difference between revisions

Jump to navigation

Jump to search

| Line 43: | Line 43: | ||

* SW2 - 0 (VME address) | * SW2 - 0 (VME address) | ||

* SW3 - 3 (VME A24 address 0x30'0000) | * SW3 - 3 (VME A24 address 0x30'0000) | ||

== Firmware sources == | |||

* git clone https://bitbucket.org/ttriumfdaq/vme-nimio32 vme-nimio32-dl-clock | |||

* git checkout dl-clock | |||

== Build firmware == | == Build firmware == | ||

Revision as of 00:24, 1 June 2025

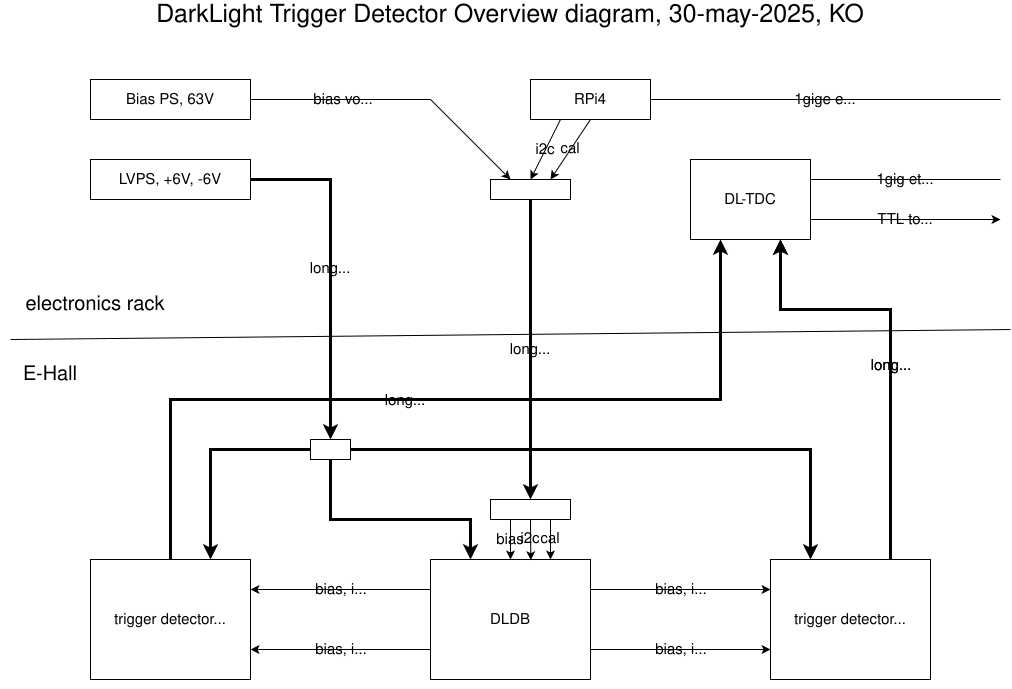

DarkLight experiment at TRIUMF

Links

- https://daq13.triumf.ca - detector facility daq station

- https://daq17.triumf.ca - MOB lab daq station

- git clone dldaq@daq00.triumf.ca/git/dlana - trigger detector analysis software

- DL-DB - trigger detector SiPM board and distribution board documentation

- https://daq00.triumf.ca/AgWiki/index.php/Chronobox - DLTDC base firmware documentation

- DL-TDC - DL-TDC special documentation

- VME-PPG32 - PPG32 documentation

- VME-NIMIO32#DL_clock_(PPG32-Rev2) - PPG32 (IO32) firmware documentation

- chronobox_firmware branch dl-tdc - DLTDC firmware git repo

- chronobox_software - DLTDC MIDAS frontend git repo

- (to be split) dldb - fedldb git repo

Drawings

File:DL-trigger-detector.drawio.pdf

File:DL-trigger-detector.drawio.pdf

DAQ

- ODB /eq/cb02/settings:

- dl_ctrl for A+B 0xC0FE

- dl_ctrl for A*B 0xC0F0

- A is grand-OR of all scintillators on the TDC-A cable (enabled by dl_trg_mask[7..0], 8 bits for the 8 scintillators)

- B is grand-OR of all scintillators on the TDC-B cable (enabled by dl_trg_mask[15..8], 8 bits for the 8 scintillators)

- each scintillator signal (A[7..0] and B[7..0]) is L*R hardwired in dl/dl.sv

- dl_tdc_mask can be used to disable each of the 32 TDC inputs (see map between TDC inputs and scintillator channels)

- there is no button to disable chronobox counters and rates for individual CB channels

PPG32-Rev2 settings

Jumper settings

- JMP1 - left (INP)

- JMP2 - left (INP)

- JMP3 - left (TTL input)

- P0 - both right (NIM output)

- P1 - both left (TTL output)

- SW1 - 0 (VME address)

- SW2 - 0 (VME address)

- SW3 - 3 (VME A24 address 0x30'0000)

Firmware sources

- git clone https://bitbucket.org/ttriumfdaq/vme-nimio32 vme-nimio32-dl-clock

- git checkout dl-clock

Build firmware

- ssh trinatdaq ### must be Ubuntu-20 to run quartus 13.1

- cd /home/olchansk/git/vme-nimio32-dl-clock/VME-NIMIO32/PPG32-Rev1

- /daq/quartus/13.1.4.182/quartus/bin/quartus

- open VME-PPG32 project, processing -> start compilation

- will produce new sof and pof files (jic file must be regenerated manually)

- load sof file into FPGA using quartus jtag programmer, then load pof file into EPCS16 flasg using srunner, see below

Load firmware

- cd ~olchansk/git/vme

- ./srunner_vme_gef.exe -id -16 /dev/null 0x300020 ### identify EPCS chip

- ./srunner_vme_gef.exe -program -16 /home/olchansk/git/vme-nimio32-dl-clock/VME-NIMIO32/PPG32-Rev1/VME-PPG32.pof 0x300020

- ./test_VMENIMIO32_gef.exe --addr 0x300000 --reboot

Check clock status

- ./test_VMENIMIO32_gef.exe --addr 0x300000 --read 9 ### read clock status, bits are as above

- ./test_VMENIMIO32_gef.exe --addr 0x300000 --write 9 0 ### reset the pll_unlocked_latch