| ID |

Date |

Author |

Topic |

Subject |

|

801

|

14 Jun 2012 |

Konstantin Olchanski | Bug Report | Cannot start/stop run through mhttpd |

> > > Revision: r5286

> > > Platform: Debian Linux 6.0.5 AMD64, with packages from squeeze-backports

>

> I found the problem only appears when I run mhttpd in scripts, whether bash or python.

> And I'm quite sure that the MIDAS environments (e.g. PATH, MIDAS_EXPTAB, MIDASSYS, etc.)

> are set in such scripts. If I start mhttpd in an xterm with or without "-D", it works

> fine.

Right. I see Debian 6.0.5 just came out hot off the presses. Would be good to fix this problem.

As a work around, can you run mhttpd without "-D", but in the background, i.e. "mhttpd -p xxx >& mhttpd.log &"?

Also what are your $PATH settings?

> So, what's the difference between invoking mhttpd directly and through a script?

As Stefan mentioned, "-D" invokes some nasty unix magic to disconnect the process from the user login session. It is

possible that this magic breaks in the latest Debian.

MIDAS "-D" does roughly the same thing as "nohup".

K.O. |

|

808

|

21 Jun 2012 |

Stefan Ritt | Bug Report | Cannot start/stop run through mhttpd |

> I agree. Somehow mhttpd cannot run mtransition. I am not super happy with this dependance on user $PATH settings and the inability to capture error messages

> from attempts to start mtransition. I am now thinking in the direction of running mtransition code by forking. But remember that mlogger and the event builder also

> have to use mtransition to stop runs (otherwise they can dead-lock). So an mhttpd-only solution is not good enough...

The way to go is to make cm_transition multi-threaded. Like on thread for each client to be contacted. This way the transition can go in parallel when there are many frontend computers for example, which will speed up

transitions significantly. In addition, cm_transition should execute a callback whenever a client succeeded or failed, so to give immediate feedback to the user. I think of something like implementing WebSockets in mhttpd for that (http://en.wikipedia.org/wiki/WebSocket).

I have this in mind since many years, but did not have time to implement it yet. Maybe on my next visit to TRIUMF?

Stefan |

|

763

|

17 Jun 2011 |

Jimmy Ngai | Forum | Cannot open input file (file too large?) |

Dear All,

I got a "Cannot open input file" error when I tried to analyze a .mid.gz file with

size over 5 GB on a 32-bit Linux. The error traced back to gzopen() in mana.c

where it returned NULL when opening the file. I understand that 32-bit Linux may

not be able to handle files with size over 2 GB. I tried to add -

D_LARGEFILE_SOURCE -D_FILE_OFFSET_BITS=64 to CFLAGS in the Makefile of MIDAS and

the analyzer, but I still got the same error. Is there any workarounds that enable

me to analyze large files on 32-bit systems?

p.s. The data file was also produced on a 32-bit Linux.

Thanks & Best Regards,

Jimmy |

|

765

|

20 Jun 2011 |

Jimmy Ngai | Forum | Cannot open input file (file too large?) |

Dear All,

Thanks Konstantin Olchanski for providing me a hint. The file can be opened now after I

changed the line:

file->gzfile = gzopen(file_name, "rb");

in function ma_open() in mana.c to the followings:

INT fd = open(file_name, O_RDONLY | O_LARGEFILE);

if (fd <= 0)

return NULL;

file->gzfile = gzdopen(fd, "rb");

No modifications to the Makefile is needed in this case.

Best Regards,

Jimmy

> Dear All,

>

> I got a "Cannot open input file" error when I tried to analyze a .mid.gz file with

> size over 5 GB on a 32-bit Linux. The error traced back to gzopen() in mana.c

> where it returned NULL when opening the file. I understand that 32-bit Linux may

> not be able to handle files with size over 2 GB. I tried to add -

> D_LARGEFILE_SOURCE -D_FILE_OFFSET_BITS=64 to CFLAGS in the Makefile of MIDAS and

> the analyzer, but I still got the same error. Is there any workarounds that enable

> me to analyze large files on 32-bit systems?

>

> p.s. The data file was also produced on a 32-bit Linux.

>

> Thanks & Best Regards,

>

> Jimmy |

|

3130

|

21 Nov 2025 |

Scott Oser | Bug Report | Cannot edit values in a subtree containing only a single array of BOOLs using the ODB web interface |

I think I've found a bug in MIDAS ...

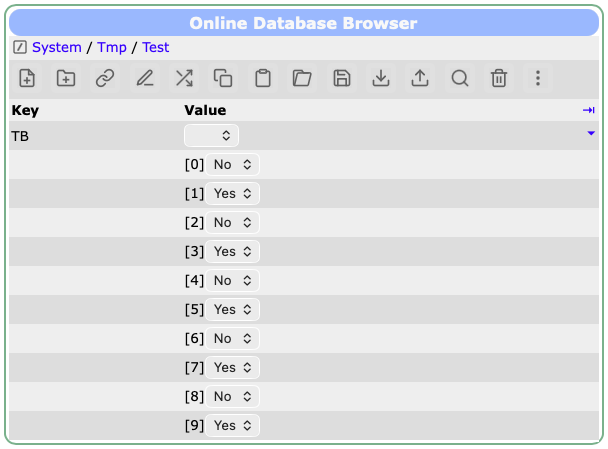

Description: If you have an ODB subtree that contains only an array of BOOLs, you cannot edit them from the ODB webpage, although you can change them using odbedit (and probably from code as well).

(If you use the dropdown menu to change any value from No to Yes, it just flips back to No immediately.)

But if you create a new key in that directory (doesn't seem to matter what), then you can edit the BOOLs from webpage. Delete that key, and once again you can't edit the BOOLs. |

|

3134

|

24 Nov 2025 |

Stefan Ritt | Bug Report | Cannot edit values in a subtree containing only a single array of BOOLs using the ODB web interface |

Can you please update to the latest develop versiokn of midas, and clear your browser cache so that the updated JavaScript midas library is loaded. Should be fixed by now. See attached screen shot where I changed every second value via the ODB editor.

Stefan

|

| Attachment 1: Screenshot_2025-11-24_at_15.32.12.png

|

|

|

3135

|

24 Nov 2025 |

Scott Oser | Bug Report | Cannot edit values in a subtree containing only a single array of BOOLs using the ODB web interface |

| Stefan Ritt wrote: |

|

Can you please update to the latest develop versiokn of midas, and clear your browser cache so that the updated JavaScript midas library is loaded. Should be fixed by now. See attached screen shot where I changed every second value via the ODB editor.

Stefan

|

Thanks --- it looks like this commit (which we just missed by four days when we last updated MIDAS) resolves the issue for us:

https://bitbucket.org/tmidas/midas/commits/6af72c1d218798064a7762bae6e65ad3407de9d1

Thanks to Ben Smith for pointing us at exactly the right commit. |

|

3139

|

25 Nov 2025 |

Konstantin Olchanski | Bug Report | Cannot edit values in a subtree containing only a single array of BOOLs using the ODB web interface |

> Thanks --- it looks like this commit resolves the issue for us ...

> Thanks to Ben Smith for pointing us at exactly the right commit

I would like to take the opportunity to encourage all to report bug fixes like this one to this mailing list.

This looks like a serious bug, many midas users would like to know when it was introduced, when found, when fixed

and who takes the credit.

K.O. |

|

756

|

15 Apr 2011 |

Jonathan Toebbe | Forum | Can't get example frontend to talk to khyt1331 kernel driver |

I'm brand new to MIDAS, and C system programming in general, so please be

gentle. I've compiled and installed MIDAS 2.3.0 on Ubuntu 10.04 LTS. I've built

the kernel driver, khyt1331.ko and installed it. It appears to be working, since

the camactest and esonetest programs included with the driver work just fine.

So I attempted to build the example experiment distributed with MIDAS, with the

following changes to the Makefile:

DRV_DIR = $(MIDASSYS)/drivers/kernel/khyt1331_26

and

DRIVER = camac

The programs build without error but when I try to start the frontend, I get:

$ ./frontend

Frontend name : CSM-Nuclear Portable DAQ Frontend

Event buffer size : 1000000

User max event size : 10000

User max frag. size : 5242880

# of events per buffer : 100

Connect to experiment...

*** buffer overflow detected ***: ./frontend terminated

======= Backtrace: =========

/lib/tls/i686/cmov/libc.so.6(__fortify_fail+0x50)[0x6de390]

/lib/tls/i686/cmov/libc.so.6(+0xe12ca)[0x6dd2ca]

/lib/tls/i686/cmov/libc.so.6(__strcpy_chk+0x44)[0x6dc644]

./frontend[0x805611f]

./frontend[0x806f656]

./frontend[0x8053d82]

/lib/tls/i686/cmov/libc.so.6(__libc_start_main+0xe6)[0x612bd6]

./frontend[0x804bb81]

======= Memory map: ========

00110000-0012d000 r-xp 00000000 08:05 7471187 /lib/libgcc_s.so.1

0012d000-0012e000 r--p 0001c000 08:05 7471187 /lib/libgcc_s.so.1

0012e000-0012f000 rw-p 0001d000 08:05 7471187 /lib/libgcc_s.so.1

00264000-00277000 r-xp 00000000 08:05 7603242 /lib/tls/i686/cmov/libnsl-2.11.1.so

00277000-00278000 r--p 00012000 08:05 7603242 /lib/tls/i686/cmov/libnsl-2.11.1.so

00278000-00279000 rw-p 00013000 08:05 7603242 /lib/tls/i686/cmov/libnsl-2.11.1.so

00279000-0027b000 rw-p 00000000 00:00 0

002db000-002dd000 r-xp 00000000 08:05 7603265

/lib/tls/i686/cmov/libutil-2.11.1.so

002dd000-002de000 r--p 00001000 08:05 7603265

/lib/tls/i686/cmov/libutil-2.11.1.so

002de000-002df000 rw-p 00002000 08:05 7603265

/lib/tls/i686/cmov/libutil-2.11.1.so

003b1000-003c6000 r-xp 00000000 08:05 7603257

/lib/tls/i686/cmov/libpthread-2.11.1.so

003c6000-003c7000 r--p 00014000 08:05 7603257

/lib/tls/i686/cmov/libpthread-2.11.1.so

003c7000-003c8000 rw-p 00015000 08:05 7603257

/lib/tls/i686/cmov/libpthread-2.11.1.so

003c8000-003ca000 rw-p 00000000 00:00 0

004ea000-004f1000 r-xp 00000000 08:05 7603261 /lib/tls/i686/cmov/librt-2.11.1.so

004f1000-004f2000 r--p 00006000 08:05 7603261 /lib/tls/i686/cmov/librt-2.11.1.so

004f2000-004f3000 rw-p 00007000 08:05 7603261 /lib/tls/i686/cmov/librt-2.11.1.so

005fb000-005fc000 r-xp 00000000 00:00 0 [vdso]

005fc000-0074f000 r-xp 00000000 08:05 7603231 /lib/tls/i686/cmov/libc-2.11.1.so

0074f000-00750000 ---p 00153000 08:05 7603231 /lib/tls/i686/cmov/libc-2.11.1.so

00750000-00752000 r--p 00153000 08:05 7603231 /lib/tls/i686/cmov/libc-2.11.1.so

00752000-00753000 rw-p 00155000 08:05 7603231 /lib/tls/i686/cmov/libc-2.11.1.so

00753000-00756000 rw-p 00000000 00:00 0

00783000-00796000 r-xp 00000000 08:05 7471302 /lib/libz.so.1.2.3.3

00796000-00797000 r--p 00012000 08:05 7471302 /lib/libz.so.1.2.3.3

00797000-00798000 rw-p 00013000 08:05 7471302 /lib/libz.so.1.2.3.3

008ab000-008c6000 r-xp 00000000 08:05 7471129 /lib/ld-2.11.1.so

008c6000-008c7000 r--p 0001a000 08:05 7471129 /lib/ld-2.11.1.so

008c7000-008c8000 rw-p 0001b000 08:05 7471129 /lib/ld-2.11.1.so

008e4000-00908000 r-xp 00000000 08:05 7603239 /lib/tls/i686/cmov/libm-2.11.1.so

00908000-00909000 r--p 00023000 08:05 7603239 /lib/tls/i686/cmov/libm-2.11.1.so

00909000-0090a000 rw-p 00024000 08:05 7603239 /lib/tls/i686/cmov/libm-2.11.1.so

08048000-0809d000 r-xp 00000000 08:11 20318114 /home/midas/online/test/frontend

0809d000-0809e000 r--p 00055000 08:11 20318114 /home/midas/online/test/frontend

0809e000-080a3000 rw-p 00056000 08:11 20318114 /home/midas/online/test/frontend

080a3000-080c5000 rw-p 00000000 00:00 0

0835f000-08380000 rw-p 00000000 00:00 0 [heap]

b7881000-b7884000 rw-p 00000000 00:00 0

b7893000-b7895000 rw-p 00000000 00:00 0

bf938000-bf94d000 rw-p 00000000 00:00 0 [stack]

Aborted

Please help me figure out what's going wrong!

Thank you,

Jon |

|

2856

|

22 Sep 2024 |

Tam Kai Chung | Bug Report | Can we convert the .mid file into .root file |

Dear experts,

I am a new user of MIDAS. I have just created some banks by a frontend.cxx code.

Now, I would like to do some analysis from the data.

I have an analyzer.cxx code (A very simple one without complicated routine).

I try to link the analyzer.o with rmana.o and libmidas.a to create analyzer.exe

I am not sure whether I can do the analysis offline in the follow way:

analyzer.exe -i run00001.mid -o run00001.root

When I run this command, I get the following error:

Error in <TClass::LoadClassInfo>: no interpreter information for class TSocket is available even though it has a TClass initialization routine.

I am using root 6.30

Any suggestion about this issue? Thank you.

Best,

Terry |

|

2858

|

24 Sep 2024 |

Konstantin Olchanski | Bug Report | Can we convert the .mid file into .root file |

"Can we convert the .mid file into .root file".

yes, you can, but the operation is under-defined. it's like asking "can I convert these stones into houses". the answer is "yes", but it involves

more than running a universal conversion program.

For this reason, I recommend against converting midas files "to root". for some types of midas data such a conversion makes no sense (i.e. alpha-g

streamed udp packets with chopped compressed waveforms).

I recommend that you analyze you data in the midas analyzer. You can start with manalyzer_example_root.cxx,

it shows how to create a ROOT histogram, how to access midas event bank data and call the TH1 "Fill" method.

Instead of filling histograms in the analyzer, you can create a ROOT TTree and fill it with data from midas data banks,

effectively you will create your own custom converter from midas to root.

The key thing is that it has to be a custom converter, because only you know the meaning of midas bank data

and how it should be best stored in a root tree.

K.O. |

|

1175

|

22 Apr 2016 |

Wes Gohn | Bug Report | Calling external script from sequencer |

Can the MIDAS Sequencer call an external script? It seems that it should be able to. I have a simple

test script to do so. It claims to execute, but the bash script never appears to be executed. Any

suggestions?

1 COMMENT "This is a MSL test file"

2 RUNDESCRIPTION "Test run"

3

4 LOOP setting, 1,2, 3

5 SCRIPT test_wheel.sh ,$setting

6 TRANSITION START

7 WAIT Seconds 10

8 TRANSITION STOP

9 ENDLOOP

I've also tried using an xml script with <Script params="1">test_wheel.sh</Script>, but with the same

result.

Thanks! |

|

1176

|

22 Apr 2016 |

Wes Gohn | Bug Report | Calling external script from sequencer |

Nevermind. I just had to give it a path to my script. Now it's fine.

> Can the MIDAS Sequencer call an external script? It seems that it should be able to. I have a simple

> test script to do so. It claims to execute, but the bash script never appears to be executed. Any

> suggestions?

>

> 1 COMMENT "This is a MSL test file"

> 2 RUNDESCRIPTION "Test run"

> 3

> 4 LOOP setting, 1,2, 3

> 5 SCRIPT test_wheel.sh ,$setting

> 6 TRANSITION START

> 7 WAIT Seconds 10

> 8 TRANSITION STOP

> 9 ENDLOOP

>

> I've also tried using an xml script with <Script params="1">test_wheel.sh</Script>, but with the same

> result.

>

> Thanks! |

|

1872

|

03 Apr 2020 |

Francesco Renga | Info | CLOCK_REALTIME on MacOS |

Dear all,

I'm trying to compile MIDAS on MacOS 10.10 and I get this error:

/Users/francesco/MIDAS/midas/src/system.cxx:3187:18: error: use of undeclared identifier

'CLOCK_REALTIME'

clock_settime(CLOCK_REALTIME, <m);

Is it related to my (old) version of MacOS? Can I fix it somehow?

Thank you,

Francesco |

|

1873

|

03 Apr 2020 |

Stefan Ritt | Info | CLOCK_REALTIME on MacOS |

> Dear all,

> I'm trying to compile MIDAS on MacOS 10.10 and I get this error:

>

> /Users/francesco/MIDAS/midas/src/system.cxx:3187:18: error: use of undeclared identifier

> 'CLOCK_REALTIME'

> clock_settime(CLOCK_REALTIME, <m);

>

> Is it related to my (old) version of MacOS? Can I fix it somehow?

>

> Thank you,

> Francesco

If I see this correctly, you need at least MacOSX 10.12. If you can't upgrade, you can just remove line 3187

from system.cxx. This function is only used in an online environment, where you would run a frontend on your

Mac, which you probably don't do. So removing it does not hurt you.

Stefan |

|

1886

|

25 Apr 2020 |

Konstantin Olchanski | Info | CLOCK_REALTIME on MacOS |

> > /Users/francesco/MIDAS/midas/src/system.cxx:3187:18: error: use of undeclared identifier

> > 'CLOCK_REALTIME'

> > clock_settime(CLOCK_REALTIME, <m);

> >

> > Is it related to my (old) version of MacOS? Can I fix it somehow?

I think the "set clock" function is a holdover from embedded operating systems

that did not keep track of clock time, i.e. VxWorks, and similar. Here a midas program

will get the time from the mserver and set it on the local system. Poor man's ntp,

poor man's ntpd/chronyd.

We should check if this function is called by anything, and if nothing calls it, maybe remove it?

K.O. |

|

1890

|

26 Apr 2020 |

Stefan Ritt | Info | CLOCK_REALTIME on MacOS |

> > > /Users/francesco/MIDAS/midas/src/system.cxx:3187:18: error: use of undeclared identifier

> > > 'CLOCK_REALTIME'

> > > clock_settime(CLOCK_REALTIME, <m);

> > >

> > > Is it related to my (old) version of MacOS? Can I fix it somehow?

>

> I think the "set clock" function is a holdover from embedded operating systems

> that did not keep track of clock time, i.e. VxWorks, and similar. Here a midas program

> will get the time from the mserver and set it on the local system. Poor man's ntp,

> poor man's ntpd/chronyd.

>

> We should check if this function is called by anything, and if nothing calls it, maybe remove it?

>

> K.O.

It's called in mfe.cxx via cm_synchronize:

/* set time from server */

#ifdef OS_VXWORKS

cm_synchronize(NULL);

#endif

This was for old VxWorks systems which had no ntp/crond. Was asked for by Pierre long time ago. I don't use it

(have no VxWorks). We can either remove it completely, or remove just the MacOSX part and just exit the program

if called with an error message "not implemented on this OS".

Stefan |

|

447

|

27 Feb 2008 |

Konstantin Olchanski | Info | CAMAC register_cnaf_callback() - removed from libmidas |

> > Affected files:

> > Makefile (add cnaf_callback.o)

> That's a good idea.

> To make things a bit easier, I modified the midas\examples\experiment\fronted.c to

> contain this call, so people should be guided by that. I also added cnaf_callback.c

> to the Makefile of the example frontend.

A request was made to remove cnaf_callback.o from libmidas as it creates a unwanted dependency on the CAMAC

hardware driver when libmidas.so is used in programs that do not use CAMAC.

After looking around, it appears that removing cnaf_callback.o from libmidas would not break anything critical,

other than CAMAC frontends that would fail to link with an obvious and easy to fix error.

I am leaving cnaf_callback.o in the Makefile - so it will be built and placed in linux/lib/cnaf_callback.o for anybody

who wants to use it.

svn revision 4130.

K.O. |

|

214

|

18 Aug 2005 |

Konstantin Olchanski | Info | CAMAC register_cnaf_callback() |

Some time ago, the "remote CAMAC" functionality in mfe.c was made conditional on

HAVE_CAMAC. This flag is not set by default so remote camac calls silently do

not work, unless midas is compiled in a special way. I am too lazy to compile

midas differently depending on what hardware I use, so I split

register_cnaf_callback() into a separate file and made it easy to call directly

from the user front end.

I left the HAVE_CAMAC bits in mfe.c so people who use that would see no change.

Affected files:

Makefile (add cnaf_callback.o)

midas.h (add void register_cnaf_callback(int debug);

mfe.c (move the rpc code to cnaf_callback.c, call register_cnaf_callback())

cnaf_callback.c (new file)

K.O. |

|

218

|

01 Sep 2005 |

Stefan Ritt | Info | CAMAC register_cnaf_callback() |

> Some time ago, the "remote CAMAC" functionality in mfe.c was made conditional on

> HAVE_CAMAC. This flag is not set by default so remote camac calls silently do

> not work, unless midas is compiled in a special way. I am too lazy to compile

> midas differently depending on what hardware I use, so I split

> register_cnaf_callback() into a separate file and made it easy to call directly

> from the user front end.

>

> I left the HAVE_CAMAC bits in mfe.c so people who use that would see no change.

>

> Affected files:

> Makefile (add cnaf_callback.o)

> midas.h (add void register_cnaf_callback(int debug);

> mfe.c (move the rpc code to cnaf_callback.c, call register_cnaf_callback())

> cnaf_callback.c (new file)

>

> K.O.

That's a good idea. The frontend framework should be independent of the used

hardware (CAMAC or VME or whatever). I event went further and removed the HAVE_CAMAC

completely. This means that people have to add the call to register_cnaf_callback()

explicitly into the frontend user init routine. I think this inconvenience is not a

big deal because even before that people had to add the cnaf_callback.c file

explicitely into their Makefile. So they have to be aware of that change, and then

it's not a big deal to modify the init routine as well. But this way we have mfe.c

completely independen of the DAQ hardware which is how it should be.

To make things a bit easier, I modified the midas\examples\experiment\fronted.c to

contain this call, so people should be guided by that. I also added cnaf_callback.c

to the Makefile of the example frontend. |