| ID |

Date |

Author |

Topic |

Subject |

|

3020

|

01 Apr 2025 |

Konstantin Olchanski | Bug Report | MIDAS history system not using the event timestamps ? | > I confirm that when writing out history files corresponding to the slow control event data,

> MIDAS history system timestamps the data not with the event time coming from the event data,

> but with the current time determined by [mlogger].

This is correct. The timestamp in the history file is the mlogger timestamp.

In theory we could use the ODB "last_written" timestamp, but in practice,

timestamps are 1 second granularity and the difference between the two

timestamps normally would be less than 1 second. (time to react to db_watch()).

But ODB last_written also is not the data timestamp. For remote connected clients

it includes the mserver communication delay.

What is the data timestamp, only the user knows - for some FPGA based equipments,

I can see the data timestamp being read from an FPGA register together with the data.

But back to earth.

For making history plots, 1 second granularity with a small (a few seconds) delay should be okey,

and I think the mserver timestamp is good enough.

For data analysis, you are reading history data from a history data file and you are

not constrained to using the MIDAS timestamp.

You can always include your "true" data timestamp as the first value in your data.

We do this in felaview for writing labview data to midas history in the ALPHA antihydrogen experiment at CERN.

This also anticipates your next request, can we have millisecond, microsecond, nanosecond history timestamps:

since you define your "true" data timestamp, you an make it anything you want. (I use "double" time in seconds,

64-bit IEEE-754 "double" has enough precision for microsecond granularity. FPGA based devices can have timestamps

with 10 ns or 8 ns granularity, in this case a uint64_t clock counter could be more appropriate).

K.O. |

|

3022

|

02 Apr 2025 |

Pavel Murat | Bug Report | MIDAS history system not using the event timestamps ? | > You can always include your "true" data timestamp as the first value in your data.

Are you saying that if the first data word of a history event were a timestamp,

the MIDAS history system, when plotting the time dependencies, would use that timestamp

instead of the mlogger timestamp?

if that is true, what tells MIDAS that the first data word is the timestamp?

I couldn't find a discussion of that on the page describing the history system -

https://daq00.triumf.ca/MidasWiki/index.php/History_System#Frontend_history_event

- perhaps I should be looking at a different page?

-- thanks again, regards, Pasha |

|

3023

|

02 Apr 2025 |

Konstantin Olchanski | Bug Report | MIDAS history system not using the event timestamps ? | > > You can always include your "true" data timestamp as the first value in your data.

>

> Are you saying that if the first data word of a history event were a timestamp,

> the MIDAS history system, when plotting the time dependencies, would use that timestamp

> instead of the mlogger timestamp?

>

you are correct, midas knows nothing about what you put in the history data.

what I suggested is: if you want your true data timestamp recorded in the history,

you can put it into the history data yourself, and I suggested using the 1st value,

but you can also make it the last value or the 10th value, it is up to you.

for making history plots, the history timestamp is used, as you wrote and I confirmed,

this timestamp is generated by mlogger.

what is not clear to me is why this is a problem? do you see a big difference between the

true data timestamp and the mlogger data timestamp? bigger than 1 second? (this would change

the shape of "last 10 minutes" plots (600 seconds). bigger than 1 minute? (this would change

the shape of "last 1 hour plots" (60 minutes, 3600 seconds).

that said, note that we currently store the timestamp as a DWORD 32-bit UNIX time value

which will overflow in 2038 and which is quickly becoming incompatible with the ongoing

switch to 64-bit time_t. Ubuntu-24 already build a large number of system libraries with 64-

bit time_t and building MIDAS with 32-bit time_t may soon become as difficult as building

32-bit MIDAS for 32-bit i686 VME processors. we have to move with the times.

what it means is that the history system data format will have to be updated to 64-bit

time_t and at the same time, we may try to change the timestamp from mlogger-generated to

frontend-generated.

but it is still not clear to me how that helps you, because the frontend-generated timestamp

is not the true data timestamp that you wanted. (and only you know what the true data

timestamp is and where it comes from and how to tell it to MIDAS).

K.O. |

|

1014

|

11 Jul 2014 |

Konstantin Olchanski | Info | MIDAS high speed test | We have tested operation of MIDAS using a 10GigE network connection. Using a dummy frontend

generating fake data, we can record MIDAS data to disk at at least 700 Mbytes/sec as reported by

the MIDAS status page.

Two configurations were tested, both run at at least 700Mbytes/sec sustained:

1) MIDAS mhttpd, mserver, mlogger running on the disk server machine (mlogger writes to local

disk), frontend running on remote machine (10GigE mserver connection).

2) MIDAS mhttpd, mserver, mlogger, frontend running on remote machine (mlogger writes data to

an NFS-mounted disk over a 10GigE connection).

In addition, for configuration (2), I simulated online analysis reading fresh midas files at the same

time as MIDAS writes new data. The resulting observation is that Linux seems to be giving main

priority to disk write traffic (700 Mbytes/sec) with the remaining disk bandwidth given to read traffic

(50-100Mbytes/sec). In other words, when running online data analysis on fresh data files, mlogger

continues to run at full speed (analysis does not slow down data taking).

A few problems with MIDAS were observed during this test:

a) mlogger data compression using gzip-1 has to be turned off (limits data rate to about

200Mbytes/sec). We plan to implement high speed LZO/LZ4 data compression that we expect to

keep up with a 10GigE network interface.

b) CPU use by mserver and mlogger is rather high (about 40% CPU)

c) when writing to the NFS disk, mlogger has a pause of 1-2 seconds when closing and reopening

subrun data files. To avoid a interruption in data taking, the SYSTEM event buffer has to be big

enough to ride through this pause, but stock MIDAS limits the maximum size of event buffer to 1GB

(too small), this can be easily increased to 2GB (almost big enough) and with some more work it can

be increased to 4GB, but no more because the buffer length is a 32-bit integer.

d) when writing to the NFS disk, we also see periodic 3-5 second interruptions ("write operation took

5123 ms") and we had one death of mlogger by a timeout of 60 sec.

Details of the hardware:

1) the disk server machine CPU is 3.4GHz Intel i7-4770, mobo is ASUS Z87 WS (10 SATA, 2xGigE),

RAM is 32GB DDR3-1600.

2) disk array is 8x4TB Seagate ST4000VN000-1H4168 NAS disks RAID0 (striped) configuration, raw

data read/write rate is around 1 GByte/sec, disks are directly attached to mobo (no raid card), linux

software raid.

3) the frontend machine CPU is 3.7GHz Intel i7-4820, mobo is ASUS P9X79 WS, RAM is 32GB DDR3-

1600.

4) 10GigE network is Solarflare Communications SFC9120 (both machines) with a cross-over fiber

cable (direct connection,no switches)

5) OS is up-to-date SL6.5 (both machines)

K.O. |

|

1019

|

06 Aug 2014 |

Konstantin Olchanski | Info | MIDAS high speed test | > We have tested operation of MIDAS using a 10GigE network connection. Using a dummy frontend

> generating fake data, we can record MIDAS data to disk at at least 700 Mbytes/sec as reported by

> the MIDAS status page.

>

> Details of the hardware:

>

> 1) the disk server machine CPU is 3.4GHz Intel i7-4770, mobo is ASUS Z87 WS (10 SATA, 2xGigE),

> RAM is 32GB DDR3-1600.

> 2) disk array is 8x4TB Seagate ST4000VN000-1H4168 NAS disks RAID0 (striped) configuration, raw

> data read/write rate is around 1 GByte/sec, disks are directly attached to mobo (no raid card), linux

> software raid.

>

These tests were done using a raid0 array (striped), which is not suitable for production use.

For production use, RAID5 and RAID6 is recommended. But their default configuration has severely reduced performance (50% of

RAID0) this is because internally the raid driver issues disk read operations that compete against and severely slow down the disk write

requests. This is easy to see with "iostat -x 1" - when writing to the raid array, there should be no reads from the disks. Following

changes are required to achieve maximum performance:

echo 32000 > /sys/block/md6/md/stripe_cache_size # increase internal memory buffers - because "raid write" is always "read-

modify-write", bigger buffers ensure that the reads are done from cache, not from phsyical disk

mdadm --grow --bitmap=/md6bitmap /dev/md6 # use external bitmap - if bitmap is internal, there is a large number of disk reads

competing against writes. external bitmap seems to help quite a bit.

With these settings, my RAID6 array can read and write at about 700-900 Mbytes/sec - this is comparable to RAID0 (minus 2 disks).

With this, I repeated the MIDAS performance tests - (but without 10GigE) - MIDAS can write 700 Mbytes/sec of fake data to a local

RAID6 data array. (hardware configuration is listed above).

K.O. |

|

2722

|

08 Mar 2024 |

Konstantin Olchanski | Info | MIDAS frontend for WIENER L.V. P.S. and VME crates | Our MIDAS frontend for WIENER power supplies is now available as a standalone git repository.

https://bitbucket.org/ttriumfdaq/fewienerlvps/src/master/

This frontend use the snmpwalk and snmpset programs to talk to the power supply.

Also included is a simple custom web page to display power supply status and to turn things on and off.

This frontend was originally written for the T2K/ND280 experiment in Japan.

In addition to controlling Wiener low voltage power supplies, it was also used to control the ISEG MPOD high

voltage power supplies.

In Japan, ISEG MPOD was (still is) connected to the MicroMegas TPC and is operated in a special "spark counting"

mode. This spark counting code is still present in this MIDAS frontend and can be restored with a small amount of

work.

K.o. |

|

506

|

13 Oct 2008 |

Konstantin Olchanski | Info | MIDAS drivers for Tundra tsi148 pci-vme bridge | The latest midas mvmestd.h driver for the Tundra tsi148 pci-vme bridge as used

on GEFANUC VME processors have been commited, revision 4349.

This midas drivers require the "gefvme" Linux kernel driver supplied by GEFANUC

as part of their Linux BSP. (Note that version "v7865-sdk-linux-R01.00" from

GEFANUC is mostly non-functional).

At TRIUMF have the V7865 VME processors and use the kernel driver

v7865-sdk-linux-R01.00-KO6. This driver supports these functions:

1) memory mapped access to full VME A16 and A24 address spaces and window-mapped

access to VME A32 address space. (original gefvme driver does not do

memory-mapped access)

2) DMA directly from vme to user memory, with support for multi-segment chained

transfers (original gefvme driver lacks chained transfers)

3) DMA from user memort to vme should work but is untested

4) no support for interrupts (original gefvme driver does not interrupts).

If you are interested in in using the TRIUMF driver, please contact me directly.

If you already purchased the GEFANUC BSP, I think you can use my drivers

immediately, without objection from GEFANUC.

Otherwise, I will have to do some research into the gefvme code license: since

all of the code appears to have GPL headers and identical code exists on the

internet, I expect to find that my gefvme driver can be freely distributed under

the GPL. But until then, and until it is cleared with TRIUMF management, I

cannot make my gefvme driver available for free download.

K.O. |

|

845

|

14 Dec 2012 |

Robert Casperson | Bug Report | MIDAS does not function correctly on F17 | When building MIDAS on Fedora 17 64-bit, the default zlib 1.2.5 shared library

is linked to. When recording data, the "/Logger/Channels/*/Statistics/Bytes

written" value does not get set correctly beyond the first few seconds of the

run. Occasionally, it appears to not get set at all, and mlogger aborts the run.

Installing zlib 1.2.3 in static form to /usr/local/lib (the default location),

and changing the NEED_ZLIB section of the MIDAS Makefile to the following seems

to function as a workaround:

ifdef NEED_ZLIB

CFLAGS += -DHAVE-ZLIB

LIBS += /usr/local/lib/libz.a

endif

Several Fedora 17 libraries expect zlib 1.2.5 specifically, so it seems safest

to not replace the default zlib shared library.

Some extra details are that the VME CPU is an XVB602, and the most recent GE-IP

drivers are being used for VME communication. Fedora 17 was chosen to avoid a

bug with the VGA output in Fedora 13-16. |

|

850

|

20 Dec 2012 |

Stefan Ritt | Bug Report | MIDAS does not function correctly on F17 | If is not so easy to get out of zlib how many bytes have been written actually. I used an undocumented function,

which breaks down on 64-bit systems.

I now rewrote the code in mlogger.cxx to use lseek() to "measure" actually the output file and set the values

correctly. I tried on a few systems but am not 100% sure if it works everywhere. Can you please double check?

The fix is in SVN revision 5347.

/Stefan |

|

835

|

10 Sep 2012 |

Shaun Mead | Info | MIDAS button to display image | Hi,

I've written a python script that reads some data from a file and generates a

.png image. I want to have a button on my MIDAS status page that:

- executes the script and waits for it to finish,

- then displays the image

How can I do that? I tried using the sequencer to just execute the script every

30 seconds, but I can't get it to work, and it would be better to only execute

the script on demand anyway.

I also am having trouble getting image display to work. I have the ODB keys set:

[local:oven1:S]/Custom>ls

Temperature Map& /home/deap/ovendaq/online/index.html

Images

[local:oven1:S]/Custom>ls Images/temps.png/

Background /home/deap/ovendaq/online/temps.png

And the HTML file is just this:

<img src="temps.png">

But the image won't display. It shows a "broken" picture, and when I try to view

it directly it says: Invalid custom page: Page not found in ODB.

Any help would be appreciated...

Thanks

Shaun |

|

836

|

11 Sep 2012 |

Stefan Ritt | Info | MIDAS button to display image | > Hi,

>

> I've written a python script that reads some data from a file and generates a

> .png image. I want to have a button on my MIDAS status page that:

>

> - executes the script and waits for it to finish,

> - then displays the image

>

> How can I do that? I tried using the sequencer to just execute the script every

> 30 seconds, but I can't get it to work, and it would be better to only execute

> the script on demand anyway.

>

> I also am having trouble getting image display to work. I have the ODB keys set:

>

> [local:oven1:S]/Custom>ls

> Temperature Map& /home/deap/ovendaq/online/index.html

> Images

>

> [local:oven1:S]/Custom>ls Images/temps.png/

> Background /home/deap/ovendaq/online/temps.png

>

> And the HTML file is just this:

> <img src="temps.png">

>

> But the image won't display. It shows a "broken" picture, and when I try to view

> it directly it says: Invalid custom page: Page not found in ODB.

>

> Any help would be appreciated...

>

> Thanks

> Shaun

If you use the "custom" image system, you need to use GIF images. mhttpd can dynamically create GIF

images,

with a background image and overlaid labels, bar graphs etc. But mhttpd just contains a GIF library to do

that

in memory, but no PNG library.

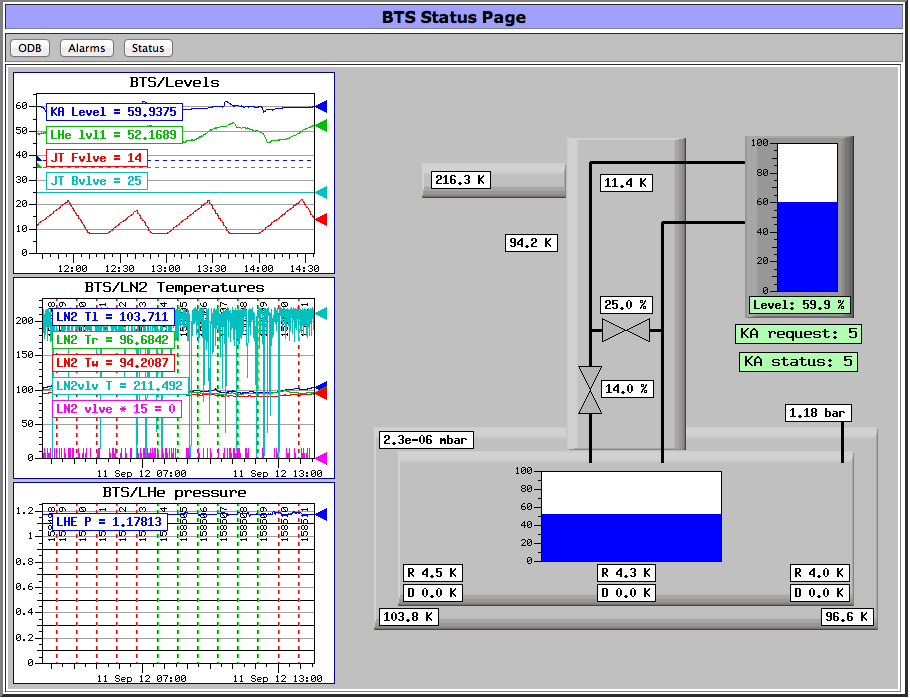

Actually I would recommend you not to use a script to create an image, but use the custom image system

to

display temperatures. In the attachment you see an page from our experiment which contains a

background image (the greyish boxes), labels (white temperature boxes), bar graphs (blue level boxes)

and history pages (left side). This is all dynamically created inside mhttpd using the custom page system

without any external script. All you have to do is to get the temperatures and levels inside the ODB via the

slow control system. If you want, I can send you the full code for that page.

Cheers,

Stefan |

| Attachment 1: Screen_Shot_2012-09-11_at_14.36.56_.png

|

|

|

2707

|

12 Feb 2024 |

Konstantin Olchanski | Info | MIDAS and ROOT 6.30 | Starting around ROOT 6.30, there is a new dependency requirement for nlohmann-json3-dev from https://github.com/nlohmann/json.

If you use a Ubuntu-22 ROOT binary kit from root.cern.ch, MIDAS build will bomb with errors: Could not find a package configuration file provided by "nlohmann_json"

Per https://root.cern/install/dependencies/ install it:

apt install nlohmann-json3-dev

After this MIDAS builds ok.

K.O. |

|

2327

|

29 Jan 2022 |

Isaac Labrie Boulay | Forum | MIDAS and GRIF-16 digitizer (Standalone Mode). | Hi all,

I was sent a version of the frontend for the TIGRESS Detector lab setup so that

I can test detectors using a GRIF-16 digitizer in standalone mode.

I followed the GRIF-16 wiki (https://grsi.wiki.triumf.ca/wiki/GRIF-16#One-

level_operation) to setup the GRIF-16 through the webpage. The digitized data is

supposed to come into my UDP port 8800 but it is never retrieved in the

frontend.

Here's the readout scheme:

// readout sequence ...

// poll_event() true (if still have data in buffer or testmsg() true)

// -> read_trigger_event() -> read_grifc_event() - re-buffers into midas events

// -> grifc_eventread() - returns single grif fragment

// -> grifc_dataread() - returns single net-pkt

Here's poll_event():

INT poll_event(INT source, INT count, BOOL test)

{

int i, have_data=0;

for(i=0; i<count; i++){

if( data_available ){ break; }

have_data = ( testmsg(data_socket, 0) > 0 );

if( have_data && !test ){ break; }

}

return( (have_data || data_available) && !test );

}

This being said, testmsg() always returns empty and "data_available" is only set

to TRUE when there's leftover data after a GRIF-C reading (I'm obviously not

using a GRIF-C).

I know that when GRIF-16 is in standalone mode, MIDAS does not change GRIF-16s

settings based on the ODB, it has to be done through the GRIF-16 webpage. Is the

user frontend code even responsible for the GRIF-16 data readout in standalone

mode? If not, could it just be that my UDP offloader is incorrectly setup?

Here are its current settings:

SETTINGS/UDP

- Offloader: ON

- Dst IP: my IP

- Dst Port: 8800 (DATA_PORT)

SETTINGS/MIDAS

- Use MIDAS: OFF

- MIDAS Hostname: my hostname

- MIDAS IP: same as Dst IP from UDP settings

- Dst Port: 8080 (I'm assuming that this is the mhttpd port)

Again, the frontend runs but I get 0 events. What might I be missing?

Thanks for helping me out!

Isaac |

|

255

|

11 May 2006 |

Konstantin Olchanski | Bug Report | MIDAS and Fedora 4 | Fellow Midasites- we are receiving reports that current Midas sources do not compile on Fedora 4 (and 5?)

with errors "invalid lvalue in assignment". It looks like the new compilers reject what looks to my eye like

perfectly valid C code that we have been writing since the beginning of C. Any suggestions on the best fix?

K.O. |

|

949

|

16 Jan 2014 |

Konstantin Olchanski | Info | MIDAS and "international characters", UTF-8 and Unicode. | I made some tests of MIDAS support for "international characters" and we seem to be in a reasonable

shape.

The standard standard is UTF-8 encoding of Unicode and the MIDAS core is believed to be UTF-8 clean -

one can use "international characters" in ODB names, in ODB values, in filenames, etc.

The web interface had some problems with percent-encoding of ODB URLs, but as of current git version,

everything seems to work okey, as long as the web browser is in the UTF-8 encoding mode. The default

mode is "Western ISO-8859-1" and javascript encodeURIComponent() is mangling some stuff making the

ODB editor not work. Switching to UTF-8 mode seems to fix that.

Perhaps we should make the UTF-8 encoding the default for mhttpd-generated web pages. This should be

okey for TRIUMF - we use English language almost exclusively, but need to check with other labs before

making such a change. I especially worry about PSI because I am not sure if and how they any of the special

German-language characters.

On the minus side, odbedit does not seem to accept non-English characters at all. Maybe it is easy to fix.

K.O. |

|

1529

|

21 May 2019 |

Thomas Lindner | Forum | MIDAS Workshop on Aug 7 | Dear MIDAS users,

We would like to announce a third MIDAS workshop at TRIUMF on Aug 7, 2019.

Stefan Ritt will again be visiting TRIUMF at this time.

The overall goal of the workshop is to present new features in MIDAS, to discuss

future changes and to hear experiences from different experiments.

We expect that some participants will connect remotely to the workshop; we will

setup a video-conferencing option. The exact time of the workshop will be

decided later and will be optimized based on the geographic distribution of

remote attendees. So please let us know if you want to attend remotely. We are

also happy for people to come in person to TRIUMF.

A (very) preliminary agenda includes

- New default mhttpd pages and new APIs for custom pages

- Conversion of MIDAS to C++

- new C++ based frontend framework (tmfe and mvodb from ALPHA-g)

- MySQL/Postgres database for storing ODB configurations

- Plans for updating history plotting

- Using MIDAS with an online trigger farm

- new C++ multithreaded flow analyzer (manalyzer from ALPHA-g)

But please suggest other topics; we also hope to hear reports from particular

experiments.

Sincerely,

Thomas (on behalf of MIDAS developers) |

|

1588

|

03 Jul 2019 |

Thomas Lindner | Forum | MIDAS Workshop on Aug 7 | Dear MIDAS users,

Here's further information on the third MIDAS workshop:

1) Workshop will take place from 1PM-5PM (Vancouver time) on Aug 7.

2) A mostly finalized agenda for the workshop is posted here:

https://indico.triumf.ca/conferenceDisplay.py?confId=2438

People are still welcome to email me if they want to present something. We should be able to add it to the schedule.

3) For those who want to participate remotely, we will be using bluejeans. The webpage for the bluejeans meeting is here:

https://bluejeans.com/462865444

4) For those at TRIUMF I will confirm the meeting room closer to the date.

Thomas

> Dear MIDAS users,

>

> We would like to announce a third MIDAS workshop at TRIUMF on Aug 7, 2019.

> Stefan Ritt will again be visiting TRIUMF at this time.

>

> The overall goal of the workshop is to present new features in MIDAS, to discuss

> future changes and to hear experiences from different experiments.

>

> We expect that some participants will connect remotely to the workshop; we will

> setup a video-conferencing option. The exact time of the workshop will be

> decided later and will be optimized based on the geographic distribution of

> remote attendees. So please let us know if you want to attend remotely. We are

> also happy for people to come in person to TRIUMF.

>

> A (very) preliminary agenda includes

>

> - New default mhttpd pages and new APIs for custom pages

> - Conversion of MIDAS to C++

> - new C++ based frontend framework (tmfe and mvodb from ALPHA-g)

> - MySQL/Postgres database for storing ODB configurations

> - Plans for updating history plotting

> - Using MIDAS with an online trigger farm

> - new C++ multithreaded flow analyzer (manalyzer from ALPHA-g)

>

> But please suggest other topics; we also hope to hear reports from particular

> experiments.

>

> Sincerely,

> Thomas (on behalf of MIDAS developers) |

|

1641

|

06 Aug 2019 |

Thomas Lindner | Forum | MIDAS Workshop on Aug 7 | Dear MIDAS users,

A final reminder about the MIDAS workshop tomorrow. A couple reminders/notes:

1) Workshop will take place from 1PM-5:30PM (Vancouver time) on Aug 7.

2) A finalized agenda for the workshop is posted here:

https://indico.triumf.ca/conferenceDisplay.py?confId=2438

Speakers should email me their talks beforehand and I will post them.

3) For those who want to participate remotely, we will be using bluejeans. The webpage for the bluejeans meeting is here:

https://bluejeans.com/462865444

I will start the connection ~20min before the start of the session; people calling in remotely might want to call early, so we can test the sound quality.

4) For those at TRIUMF, the meeting will be in the ISAC-II conference room.

Thomas

> Dear MIDAS users,

>

> Here's further information on the third MIDAS workshop:

>

> 1) Workshop will take place from 1PM-5PM (Vancouver time) on Aug 7.

>

> 2) A mostly finalized agenda for the workshop is posted here:

>

> https://indico.triumf.ca/conferenceDisplay.py?confId=2438

>

> People are still welcome to email me if they want to present something. We should be able to add it to the schedule.

>

> 3) For those who want to participate remotely, we will be using bluejeans. The webpage for the bluejeans meeting is here:

>

> https://bluejeans.com/462865444

>

> 4) For those at TRIUMF I will confirm the meeting room closer to the date.

>

> Thomas

>

>

> > Dear MIDAS users,

> >

> > We would like to announce a third MIDAS workshop at TRIUMF on Aug 7, 2019.

> > Stefan Ritt will again be visiting TRIUMF at this time.

> >

> > The overall goal of the workshop is to present new features in MIDAS, to discuss

> > future changes and to hear experiences from different experiments.

> >

> > We expect that some participants will connect remotely to the workshop; we will

> > setup a video-conferencing option. The exact time of the workshop will be

> > decided later and will be optimized based on the geographic distribution of

> > remote attendees. So please let us know if you want to attend remotely. We are

> > also happy for people to come in person to TRIUMF.

> >

> > A (very) preliminary agenda includes

> >

> > - New default mhttpd pages and new APIs for custom pages

> > - Conversion of MIDAS to C++

> > - new C++ based frontend framework (tmfe and mvodb from ALPHA-g)

> > - MySQL/Postgres database for storing ODB configurations

> > - Plans for updating history plotting

> > - Using MIDAS with an online trigger farm

> > - new C++ multithreaded flow analyzer (manalyzer from ALPHA-g)

> >

> > But please suggest other topics; we also hope to hear reports from particular

> > experiments.

> >

> > Sincerely,

> > Thomas (on behalf of MIDAS developers) |

|

2534

|

13 Jun 2023 |

Thomas Lindner | Info | MIDAS Workshop 2023 - Sept 13 | Hi All,

Thanks to everyone who filled out the doodle poll.

Based on the results we will plan to have this workshop on September 13, at 9AM-1PM (Vancouver) / 6PM-10PM (Geneva). Apologies to

those for whom this is a bad time/day; in particular for MIDAS users in Asia.

If you would like to present a report at the workshop on your experiment's MIDAS experience, then please email me (lindner@triumf.ca).

It would be great to know this in advance so that we can start preparing an agenda. Feel free to also email me if there are topics

that you would like addressed at the workshop.

Thanks,

Thomas

> Dear MIDAS users,

>

> We would like to arrange another MIDAS workshop, following on from previous successful workshops in 2015, 2017 and 2019. The

> goals of the workshop would include:

>

> - Getting updates from MIDAS developers on new features and other changes.

> - Getting reports from MIDAS users on how they are using MIDAS, what is working and what is not

> - Making plans for future MIDAS changes and improvements

>

> This would be a one-day virtual workshop, planned for about 4 hours length. The workshop will probably be after another of

> Stefan's visits to TRIUMF.

>

> If you would be interested in participating in such a workshop, please help us choose the date by filling out this doodle poll:

>

> https://doodle.com/meeting/organize/id/dBPVMQJa

>

> Please fill in the poll by June 9, if you are interested. We will announce the date soon after that.

>

> Thanks,

> Thomas |

|

2590

|

17 Aug 2023 |

Thomas Lindner | Info | MIDAS Workshop 2023 - Sept 12-13 | Dear All,

A quick update on the MIDAS workshop. Based on the number of planned talks we have made the decision to switch to a two day workshop on Sept 12 and 13

(rather than just Sept 13). We decided 4 hours was not enough time to hear all the reports and have fruitful discussions; having a much longer meeting

on a single day was a bad idea given the time zones involved.

We have a tentative agenda planned for the workshop, which you can see here:

https://indico.psi.ch/event/15025/timetable/

We are still confirming some talks, so the agenda may still change a bit. But the baseline plan will be that the workshop will be

8:30AM-12:30PM (PDT) / 5:30PM-9:30PM (CEST)

on Sept 12-13. We hope that these times still work for everyone planning to attend.

Cheers,

Thomas

> Hi All,

>

> Thanks to everyone who filled out the doodle poll.

>

> Based on the results we will plan to have this workshop on September 13, at 9AM-1PM (Vancouver) / 6PM-10PM (Geneva). Apologies to

> those for whom this is a bad time/day; in particular for MIDAS users in Asia.

>

> If you would like to present a report at the workshop on your experiment's MIDAS experience, then please email me (lindner@triumf.ca).

> It would be great to know this in advance so that we can start preparing an agenda. Feel free to also email me if there are topics

> that you would like addressed at the workshop.

>

> Thanks,

> Thomas

>

>

> > Dear MIDAS users,

> >

> > We would like to arrange another MIDAS workshop, following on from previous successful workshops in 2015, 2017 and 2019. The

> > goals of the workshop would include:

> >

> > - Getting updates from MIDAS developers on new features and other changes.

> > - Getting reports from MIDAS users on how they are using MIDAS, what is working and what is not

> > - Making plans for future MIDAS changes and improvements

> >

> > This would be a one-day virtual workshop, planned for about 4 hours length. The workshop will probably be after another of

> > Stefan's visits to TRIUMF.

> >

> > If you would be interested in participating in such a workshop, please help us choose the date by filling out this doodle poll:

> >

> > https://doodle.com/meeting/organize/id/dBPVMQJa

> >

> > Please fill in the poll by June 9, if you are interested. We will announce the date soon after that.

> >

> > Thanks,

> > Thomas |

|